As of August 27, 2004 the Fast Ethernet Consortium Clause 25 Physical Medium Dependent Conformance Test Suite version 3.2 has been superseded by the release of the Clause 25 Physical Medium Dependent Conformance Test Suite version 3.21. This document along with earlier versions, are available on the Fast Ethernet Consortium test suite archive page.

Please refer to the following site for both current and superseded test suites:

http://www.iol.unh.edu/testsuites/ethernet/archive.html

© 2004 University of New Hampshire InterOperability Laboratory

# TABLE OF CONTENTS

| TABLE OF CONTENTS                                            | 2  |

|--------------------------------------------------------------|----|

| MODIFICATION RECORD                                          | 3  |

| ACKNOWLEDGMENTS                                              | 4  |

| INTRODUCTION                                                 | 5  |

| GROUP 1: ACTIVE OUTPUT INTERFACE (AOI) TESTS                 | 7  |

| TEST #25.1.1 – DIFFERENTIAL OUTPUT VOLTAGE                   | 8  |

| TEST #25.1.2 – RISE AND FALL TIMES                           | 10 |

| TEST #25.1.3 – DUTY CYCLE DISTORTION                         | 12 |

| Test #25.1.4 – Transmit Jitter                               | 14 |

| TEST #25.1.5 – WAVEFORM OVERSHOOT                            | 15 |

| TEST #25.1.6 – TRANSMITTER RETURN LOSS                       | 17 |

| Test #25.1.7 – Transmitter Open Circuit Inductance           | 19 |

| Test #25.1.8 – Transmit Clock Frequency                      | 20 |

| GROUP 2: ACTIVE INPUT INTERFACE (AII)                        | 21 |

| Test #25.2.1 – Differential Input Impedance                  | 22 |

| TEST #25.2.2 – ADAPTIVE EQUALIZATION                         | 24 |

| TEST #25.2.3 – BASELINE WANDER CORRECTION                    | 26 |

| TEST #25.2.4 – BIT ERROR RATE VERIFICATION                   | 28 |

| TEST SUITE APPENDICES                                        | 30 |

| APPENDIX 25.A – TEST SETUP IMPLEMENTATION EXAMPLES           | 31 |

| APPENDIX 25.B – TRANSMIT JITTER MEASUREMENT                  | 37 |

| Appendix 25.C – Link Model                                   | 42 |

| APPENDIX 25.D – BIT ERROR RATE MEASUREMENT                   | 49 |

| APPENDIX 25.E – RETURN LOSS INCIDENT WAVE POWER CALCULATIONS | 55 |

## **MODIFICATION RECORD**

February 25, 2004 (Version 3.2) Long Awaited Update Jon Beckwith: Added test 25.1.8, Transmit Clock Frequency Fixed the procedure of test 25.1.7 Fixed equation 25.C-5 Removed support for STP in test 25.1.1 Minor editorial and formatting changes. Added Appendix E

- May 28, 2003 • Jon Beckwith: Updated references to reflect latest standards

- February 13, 2003 • Jon Beckwith: Changed format to be consistent with other IOL test suites.

- September 9, 1999 (Version 3.1) • Added tests 25.2.2, 25.2.3, 25.2.4, Appendix A, C, and D. Adam Healey:

- June 7, 1998 (Version 3.0) •

## ACKNOWLEDGMENTS

The University of New Hampshire would like to acknowledge the efforts of the following individuals in the development of this test suite.

| Andy Baldman     | University of New Hampshire |

|------------------|-----------------------------|

| Jon Beckwith     | University of New Hampshire |

| Adam Healey      | University of New Hampshire |

| Peter Keefe      | University of New Hampshire |

| Eric Lynskey     | University of New Hampshire |

| Bob Noseworthy   | University of New Hampshire |

| Gary Pressler    | University of New Hampshire |

| Nathan Bourgoine | University of New Hampshire |

Fast Ethernet Consortium

The University of New Hampshire's InterOperability Laboratory (IOL) is an institution designed to improve the interoperability of standards based products by providing an environment where a product can be tested against other implementations of a standard. This particular suite of tests has been developed to help implementers evaluate the functionality of the Physical Medium Dependent (PMD) sublayer of their 100Base-Tx products.

These tests are designed to determine if a product conforms to specifications defined in the IEEE 802.3 standard. Successful completion of all tests contained in this suite does not guarantee that the tested device will operate with other devices. However, combined with satisfactory operation in the IOL's interoperability test bed, these tests provide a reasonable level of confidence that the Device Under Test (DUT) will function properly in many 100Base-Tx environments.

The tests contained in this document are organized in such a manner as to simplify the identification of information related to a test, and to facilitate in the actual testing process. Tests are organized into groups, primarily in order to reduce setup time in the lab environment, however the different groups typically also tend to focus on specific aspects of device functionality. A three-part numbering system is used to organize the tests, where the first number indicates the clause of the IEEE 802.3 standard on which the test suite is based. The second and third numbers indicate the test's group number and test number within that group, respectively. This format allows for the addition of future tests to the appropriate groups without requiring the renumbering of the subsequent tests.

The test definitions themselves are intended to provide a high-level description of the motivation, resources, procedures, and methodologies pertinent to each test. Specifically, each test description consists of the following sections:

### Purpose

The purpose is a brief statement outlining what the test attempts to achieve. The test is written at the functional level.

### References

This section specifies source material *external* to the test suite, including specific subclauses pertinent to the test definition, or any other references that might be helpful in understanding the test methodology and/or test results. External sources are always referenced by number when mentioned in the test description. Any other references not specified by number are stated with respect to the test suite document itself.

### **Resource Requirements**

The requirements section specifies the test hardware and/or software needed to perform the test. This is generally expressed in terms of minimum requirements, however in some cases specific equipment manufacturer/model information may be provided.

### Last Modification

This specifies the date of the last modification to this test.

### Discussion

The discussion covers the assumptions made in the design or implementation of the test, as well as known limitations. Other items specific to the test are covered here.

### **Test Setup**

The setup section describes the initial configuration of the test environment. Small changes in the configuration should not be included here, and are generally covered in the test procedure section, below.

### Procedure

The procedure section of the test description contains the systematic instructions for carrying out the test. It provides a cookbook approach to testing, and may be interspersed with observable results.

### **Observable Results**

This section lists the specific observables that can be examined by the tester in order to verify that the DUT is operating properly. When multiple values for an observable are possible, this section provides a short discussion on how to interpret them. The determination of a pass or fail outcome for a particular test is generally based on the successful (or unsuccessful) detection of a specific observable.

### **Possible Problems**

This section contains a description of known issues with the test procedure, which may affect test results in certain situations. It may also refer the reader to test suite appendices and/or whitepapers that may provide more detail regarding these issues.

## **GROUP 1: ACTIVE OUTPUT INTERFACE (AOI) TESTS**

### **Overview:**

This group of tests verifies several of the electrical specifications of the 100Base-Tx Physical Medium Dependent sublayer outlined in clause 25 of the IEEE 802.3-2002 standard.

### Scope:

All of the tests described in this section have been implemented and are currently active at the University of New Hampshire InterOperability Lab.

### Test #25.1.1 – Differential Output Voltage

**Purpose:** To verify that the differential output voltage of the device under test (DUT) is within the conformance limits.

#### **References:**

- [1] IEEE Std 802.3-2002, clause 25

- [2] ANSI X3.263-1995, section 9.1.2.2

- [3] Ibid., Figure 9-1

- [4] Ibid., Informative Annex J

Resource Requirements: Refer to Appendix 25.A

Last Modification: November 10, 2003 (Version 2.5)

#### **Discussion:**

Reference [1] describes the operation of the Physical Medium Dependent (PMD) sublayer for 100Base-Tx devices. This clause incorporates ANSI X3.263-1995, by reference, with the exceptions listed in 25.4. Reference [2] defines the differential output voltage at the Active Output Interface (AOI) for operation over unshielded twisted pair (UTP).

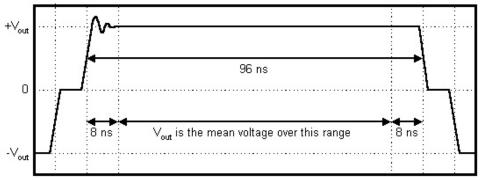

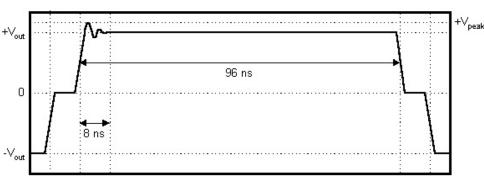

The differential output voltage,  $V_{out}$ , is defined to be the intersection of the straight line best fit for amplitude with the vertical line indicating the start of the transition from 0V to  $V_{out}$ . The reference for this measurement is defined to be an output waveform consisting of 14 bit times of no transition preceded by a transition from 0V to  $V_{out}$ .

The definition of the reference waveform was made with the assumption that the DUT would be sending scrambled, MLT-3 encoded /H/ code-groups. While this is normal for an FDDI device, it is not straightforward to get a 100BASE-TX device to generate this sequence. A 100BASE-TX device normally generates scrambled, MLT-3 encoded /I/ code-groups in which one may find 12 bit times of no transition preceded by a transition from 0V to  $V_{out}$ . This waveform is adopted as the reference.

The term "straight line best fit" in the definition of  $V_{out}$  is ambiguous. First, the region over which the fit is to be made is not defined. For this measurement, the range has been chosen to be from 8ns past the point where the signal rise crosses 50% of  $V_{out}$  to 8ns before the signal fall crosses 50% of  $V_{out}$ . These points were chosen to minimize the effect that the transient response has on the "fit". Second, it is not clear from [3] that the fit is allowed to have non-zero slope. A comparable measurement made in [4] takes  $V_{out}$  to be the mean voltage at the center of the eye. For this measurement,  $V_{out}$  is taken to be mean voltage in the aforementioned range.

Note that by taking the mean voltage, the intersection of the best fit straight line with the vertical line indicating the start of the transition from 0V to  $V_{out}$  is irrelevant. This is good because depending on the waveform properties, the start of the transition may be difficult to accurately determine.

Figure 25.1.1-1 summarizes the differential output voltage measurement considerations.

Figure 25.1.1-1: Differential output voltage reference waveform

For UTP support, the magnitude of  $V_{out}$  shall be between 950mV and 1050mV. The signal amplitude symmetry, defined as the ratio of the magnitudes of  $+V_{out}$  and  $-V_{out}$  shall be within the limits:

$$98\% \le \left| \frac{+\mathrm{V}_{\mathrm{out}}}{-\mathrm{V}_{\mathrm{out}}} \right| \le 102\%$$

Test Setup: Refer to Appendix 25.A.

#### **Procedure:**

- 1. Configure the DUT for 100BASE-TX operation. Ensure that the DUT is sending scrambled, MLT-3 encoded /I/ code-groups.

- 2. Configure the DSO to capture the waveform depicted in figure 25.1.1-1. Measure  $+V_{out}$ .

- 3. For enhanced accuracy, repeat step 2 multiple times and average the voltages measured at each point.

- 4. Configure the DSO to capture the waveform depicted in figure 25.1.1-1 but with opposite polarity. Measure  $-V_{out}$ .

- 5. For enhanced accuracy, repeat step 4 multiple times and average the voltages measured at each point.

- 6. Compute the signal amplitude symmetry.

#### **Observable Results:**

- a. The magnitude of  $V_{out}$  shall be between 950mV and 1050mV.

- b. The signal amplitude symmetry shall be between 98% and 102%.

Possible Problems: None.

### Test #25.1.2 – Rise and Fall Times

**Purpose:** To verify that the response times of the device under test (DUT) are within the conformance limits.

#### **References:**

- [1] IEEE Std 802.3-2002, clause 25

- [2] ANSI X3.263-1995, section 9.1.6

Resource Requirements: Refer to Appendix 25.A

Last Modification: November 10, 2003 (Version 2.5)

#### **Discussion:**

Reference [1] describes the operation of the physical medium dependent (PMD) sublayer for 100Base-Tx devices. This clause incorporates ANSI X3.263-1995, by reference, with the exceptions listed in 25.4. Reference [2] defines the rise and fall times at the Active Output Interface (AOI).

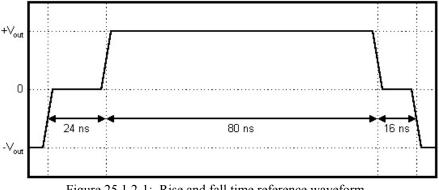

Signal rise is defined as a transition from the baseline voltage to either  $+V_{out}$  or  $-V_{out}$ . Signal fall is defined as a transition from either  $+V_{out}$  or  $-V_{out}$  to the baseline voltage. The signal rise and fall times are defined to be the time difference between the points where the signal transition crosses 10% and 90% of  $V_{out}$ .

The standard does not define a reference waveform for rise and fall time measurements. The reference waveform is chosen to be the longest pulse that follows and is followed by at least two consecutive symbols at the baseline voltage. A waveform generated in the course of transmitting scrambled, MLT-3 encoded /I/ code-groups that meets these requirements is depicted in figure 25.1.2-1. This waveform will have amplitude V<sub>out</sub> as measured in test 25.1.1 and will have signal rise and fall that is minimally affected by inter-symbol interference.

Figure 25.1.2-1: Rise and fall time reference waveform.

All measured rise and fall times shall be between 3ns and 5ns. Furthermore, the differences between all measured rise and fall times, the rise and fall time symmetry, shall not exceed 0.5ns.

**Test Setup:** Refer to Appendix 25.A.

#### **Procedure:**

- 1. Configure the DUT for 100BASE-TX operation. Ensure the DUT is transmitting scrambled, MLT-3 encoded /I/ code-groups.

- 2. Configure the DSO to capture the waveform depicted in figure 25.1.2-1. Measure the rise and fall times of the pulse.

- 3. For enhanced accuracy, repeat step 2 multiple times and average the values measured for each edge.

- 4. Configure the DSO to capture the waveform depicted in figure 25.1.2-1 but with opposite polarity. Measure the rise and fall times of the pulse.

- 5. For enhanced accuracy, repeat step 4 multiple times and average the values measured at each edge.

- 6. Compute the differences between all measured rise and fall times.

#### **Observable Results:**

- a. All measured rise and fall times shall be between 3ns and 5ns.

- b. The rise and fall time symmetry shall not exceed 0.5ns.

Possible Problems: None.

### Test #25.1.3 – Duty Cycle Distortion

Purpose: To verify that the duty cycle distortion of the device under test (DUT) is below the conformance limit.

#### **References:**

- [1] IEEE Std 802.3-2002, clause 25

- [2] ANSI X3.263-1995, section 9.1.8

Resource Requirements: Refer to Appendix 25.A

Last Modification: November 10, 2003 (Version 2.5)

#### **Discussion:**

Reference [1] describes the operation of the physical medium dependent (PMD) sublayer for 100Base-Tx devices. This clause incorporates ANSI X3.263-1995, by reference, with the exceptions listed in 25.4. Reference [2] defines the duty cycle distortion (DCD) at the Active Output Interface (AOI).

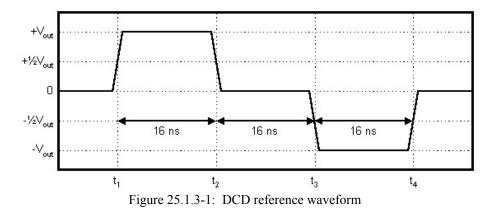

The reference waveform for the DCD measurement is depicted in figure 25.1.3-1 (indicated pulse widths are nominal values). DCD shall be measured at the points where the four successive MLT-3 transitions generated by a 01010101 NRZ bit sequence cross 50% of  $V_{out}$ . While the 01010101 NRZ sequence occurs several times in a stream of scrambled /I/ code-groups, the MLT-3 sequence that follows and is followed by at least two consecutive symbols at the baseline voltage is chosen as the reference. This minimizes any inter-symbol interference that would affect signal rise and fall.

The deviations of the 50% crossing times from a best fit grid of 16ns spacing shall not exceed  $\pm 0.25$ ns. This requirement is easily verified in terms of a peak-to-peak specification. Given the 50% crossing times  $t_n$  (refer to figure 25.1.3-1), compute  $e_m$ .

$\begin{array}{l} e_1 = t_2 - t_1 - 16ns \\ e_2 = t_3 - t_2 - 16ns \\ e_3 = t_4 - t_3 - 16ns \\ e_4 = t_3 - t_1 - 32ns \\ e_5 = t_4 - t_2 - 32ns \\ e_6 = t_4 - t_1 - 48ns \end{array}$

The peak magnitude of  $e_m$  is the peak-to-peak DCD. The peak-to-peak DCD shall not exceed 0.5ns.

Test Setup: Refer to Appendix 25.A.

#### **Procedure:**

- 1. Configure the DUT for 100BASE-TX operation. Ensure the DUT is transmitting scrambled, MLT-3 encoded /I/ code-groups.

- 2. Configure the DSO to capture the waveform depicted in figure 25.1.3-1. Measure the times at which the signal transitions cross 50% of  $V_{out}$ .

- 3. Compute  $e_1$  through  $e_6$ .

- 4. For enhanced accuracy, repeat steps 2 and 3 multiple times and average the voltages measured at each point.

- 5. Compute the peak-to-peak DCD.

**Observable Results:** The peak-to-peak DCD shall not exceed 0.5ns.

Possible Problems: None.

### Test #25.1.4 – Transmit Jitter

Purpose: To verify that the total transmit jitter of the device under test (DUT) is below the conformance limit.

#### **References:**

- [1] IEEE Std 802.3-2002, clause 25

- [2] ANSI X3.263-1995, sections 9.1.9

- [3] ANSI X3.263-1995, annex J

**Resource Requirements:** Refer to Appendix 25.A.

Last Modification: November 10, 2003 (Version 2.5)

#### **Discussion:**

Reference [1] describes the operation of the physical medium dependent (PMD) sublayer for 100Base-Tx devices. This clause incorporates ANSI X3.263-1995, by reference, with the exceptions listed in 25.4. Reference [2] defines the transmit jitter at the Active Output Interface (AOI).

The ANSI standard states that the transmit jitter measurement shall be performed on scrambled, MLT-3 encoded /H/ code-groups. The transmit jitter measured, including contributions from duty cycle distortion and baseline wander, shall not exceed 1.4ns peak-to-peak. Note the subclause 25.4.5 states that the transmit jitter measurement may also be performed on scrambled, MLT-3 encoded /I/ code-groups.

Even though a reference pattern and a peak-to-peak value are defined, the transmit jitter specification is not complete. Jitter is a statistical phenomenon and a peak-to-peak value is meaningless unless it is related to some probability, usually the bit error rate (BER). Since neither the ANSI standard nor clause 25 specify a target BER for 100BASE-TX, a BER of  $10^{-8}$  is assumed.

Also, it is not clear whether the transmit clock or a recovered clock is to be used as the timing reference. The principal difference between the two is the amount of the low frequency jitter that appears in the measurement. The recovered clock is typically generated by a phase-locked loop (PLL) which tracks jitter below its bandwidth. This is equivalent to measuring the jitter at the output of a high-pass filter. As the bandwidth of the PLL decreases, the difference between the transmit clock and the recovered clock also decreases. It is assumed that the reference for this measurement is the transmit clock. If the transmit clock is not available, a very narrow bandwidth PLL shall be used to generate the timing reference.

There are a variety of instruments and techniques that can be used to measure jitter. A DSO-based approach that does not require access to the transmit clock is presented in appendix 25.B. A popular method of visualizing jitter on the waveform is the eye mask, defined in [3]. A plot is included in the report, and while the eye diagram is a good indicator of the jitter, the value seen in the report is the peak-to-peak value, which is not obtained simply by looking at the eye diagram. In fact, the eye diagram may fail while the peak-to-peak value passes, and vice versa.

#### Test Setup: Refer to Appendix 25.A

#### **Procedure:**

- 1. Configure the DUT for 100BASE-TX operation. Ensure that the DUT is sending scrambled, MLT-3 encoded /I/ code-groups.

- 2. Measure the peak-to-peak transmit jitter at a BER of  $10^{-8}$  using the method presented in appendix 25.B.

**Observable Results:** The peak-to-peak transmit jitter shall not exceed 1.4ns at a BER of 10<sup>-8</sup>.

Possible Problems: None.

Fast Ethernet Consortium

### Test #25.1.5 – Waveform Overshoot

Purpose: To verify that the waveform overshoot of the device under test (DUT) is below the conformance limit.

#### **References:**

- [1] IEEE Std 802.3-2002, clause 25

- [2] ANSI X3.263-1995, section 9.1.3

Resource Requirements: Refer to Appendix 25.A.

Last Modification: November 10, 2003 (Version 2.5)

#### **Discussion:**

Reference [1] describes the operation of the physical medium dependent (PMD) sublayer for 100Base-Tx devices. This clause incorporates ANSI X3.263-1995, by reference, with the exceptions listed in 25.4. Reference [2] defines the waveform overshoot at the Active Output Interface (AOI).

The waveform overshoot is defined as the percentage excursion of the differential signal transition beyond its final adjusted value,  $V_{out}$ , during the symbol interval (8ns) following the signal transition. While no reference waveform is defined for the measurement, the same waveform used to measure  $V_{out}$  (refer to test 25.1.1) is assumed.

Note that the end of the signal transition may be difficult to accurately determine. A more straightforward approach is adopted which measures the peak excursion in the symbol interval following the point where the signal rise crosses 50% of  $V_{out}$ . The peak excursion is called  $V_{peak}$ .

The waveform overshoot shall not exceed 5%. In terms of  $V_{peak}$ , the following inequality shall be satisfied.

$5\% \geq \frac{V_{peak} - V_{out}}{V_{out}} \times 100\%$

Figure 25.1.5-1: Waveform overshoot reference waveform

**Test Setup:** Refer to Appendix 25.A.

#### **Procedure:**

- 1. Configure the DUT for 100BASE-TX operation. Ensure that the DUT is sending scrambled, MLT-3 encoded /I/ code-groups.

- 2. Configure the DSO to capture the waveform depicted in figure 25.1.5-1. Measure +V<sub>peak</sub>. Compute the waveform overshoot.

- 3. For enhanced accuracy, repeat step 2 multiple times and average the peak voltages measured.

- Configure the DSO to capture the waveform depicted in figure 25.1.5-1 but with opposite polarity. Measure –V<sub>peak</sub>. Compute the waveform overshoot.

- 5. For enhanced accuracy, repeat step 4 multiple times and average the peak voltages measured.

Observable Results: The waveform overshoot shall not exceed 5%.

Possible Problems: None.

### Test #25.1.6 – Transmitter Return Loss

**Purpose:** To verify that the return loss at the transmitter of the device under test (DUT) is above the conformance limit.

#### **References:**

- [1] IEEE Std 802.3-2002, clause 25

- [2] ANSI X3.263-1995, section 9.1.5

Resource Requirements: Refer to Appendix 25.A.

Last Modification: November 10, 2003 (Version 2.5)

#### **Discussion:**

Reference [1] describes the operation of the physical medium dependent (PMD) sublayer for 100Base-Tx devices. This clause incorporates ANSI X3.263-1995, by reference, with the exceptions listed in 25.4. Reference [2] defines the return loss at the Active Output Interface (AOI).

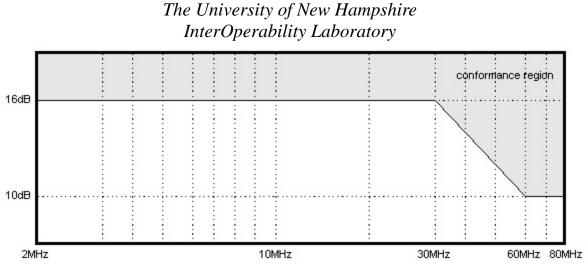

The ANSI standard states that the return loss at the AOI shall be above the limit line depicted in figure 25.1.6-1. Return loss, as defined in test 25.2.1, is the magnitude of the reflection coefficient expressed in decibels. The reflection coefficient,  $\Gamma$ , is the ratio of the voltage in the reflected wave to the voltage in the incident wave. In this case, the observed reflection is the sum of the actual reflection and the voltage generated by the transmitter of the DUT. This additional voltage introduces an error into the measured reflection coefficient,  $\Gamma_e$ :

$$\Gamma_{\rm e} = \frac{\mathbf{V}_{\rm R} + \mathbf{V}_{\rm T}}{\mathbf{V}_{\rm I}} = \Gamma + \frac{\mathbf{V}_{\rm T}}{\mathbf{V}_{\rm I}}$$

Note that  $V_R$  is the voltage in the reflected wave and  $V_T$  is the voltage transmitted by the DUT.  $V_I$  is the voltage in the incident wave. The ratio of  $V_T$  to  $V_I$  is the error in the reflection coefficient measurement. It can be shown that the resulting error in the return loss calculation is:

$$e(dB) = -20 \cdot \log_{10} \left( 1 + \frac{V_T}{V_I} \cdot \frac{1}{\Gamma} \right) = -20 \cdot \log_{10} (1+r)$$

Table 25.1.6-1 shows e as a function of r. Figure 25.1.6-1 shows that the minimum conformant return loss is 10dB, which corresponds to a reflection coefficient of 0.32. In order to assure the error in the return loss measurement does not exceed 0.5dB for any conformant return loss, the ratio of  $V_T$  to  $V_I$  must be less than  $\Gamma \cdot r = 0.32 \cdot 0.05 = 0.016$ . This is easily achieved for  $V_I$  greater than 100mV.

0.05 0.09 0.06 0.07 0.08 0.1 0.2 0.3 0.4 r e (dB) -0.42 -0.51 -0.59 -0.67 -0.75 -0.83 -1.58 -2.28 -2.92

Table 25.1.6-1: Error in the return loss calculation as a function of r.

Figure 25.1.6-1: Return loss limit as a function of frequency.

As mentioned in test 25.2.1, return loss cannot be computed without a specified source impedance  $Z_S$ .  $Z_S$  is defined to be  $100\Omega \pm 15\Omega$ .  $Z_S$  is primarily resistive with a phase angle magnitude less than 3° in the frequency range of 2MHz to 80MHz.

Test Setup: Refer to Appendix 25.A.

#### **Procedure:**

- 1. Configure the DUT for 100BASE-TX operation. Ensure that the DUT is sending scrambled, MLT-3 encoded /I/ code-groups.

- 2. Measure the reflection coefficient at the transmitter in the frequency range of 2MHz to 80MHz.

- 3. Compute the return loss for a  $Z_S$  of 85 $\Omega$  and a  $Z_S$  of 115 $\Omega$ . Assume  $Z_S$  to be completely resistive.

**Observable Results:** The return loss at the AOI shall not fall below the limit line depicted in figure 25.1.6-1.

Possible Problems: None.

### Test #25.1.7 – Transmitter Open Circuit Inductance

**Purpose:** To verify that the open circuit inductance at the transmitter of the device under test (DUT) is above the conformance limit.

#### **References:**

- [1] IEEE Std 802.3-2002, clause 25

- [2] ANSI X3.263-1995, section 9.1.7

- [3] ANSI X3.263-1995, figure 9-2

Resource Requirements: Refer to Appendix 25.A.

Last Modification: November 10, 2003 (Version 2.1)

#### **Discussion:**

Reference [1] describes the operation of the physical medium dependent (PMD) sublayer for 100Base-Tx devices. This clause incorporates ANSI X3.263-1995, by reference, with the exceptions listed in 25.4. Reference [2] defines the open circuit inductance (OCL) at the Active Output Interface (AOI).

The ability of a 100BASE-TX receiver to track baseline wander is dependent on the worst case droop allowed by the transmitter sending the stream. This droop is a function of the OCL of the transmitter. The value of the OCL varies with bias current, temperature, and manufacturing distributions. A worst case baseline wander frame creates a DC bias in the transformer of the AOI. A minimum OCL must be maintained in the presence of this bias current, so that the change in the droop of the data frames is minimized. The standard specifies that the OCL must be at least 350  $\mu$ H for any DC bias current between 0 and 8 mA.

A test setup is described in [3]. However, an alternate test setup has been devised using available equipment. Reference [3] specifies that the measurement be made with an impedance analyzer producing a 100 mV<sub>rms</sub> test signal at 100 kHz. This has been substituted with an inductance meter, which takes its measurements using a 715  $\mu$ A<sub>rms</sub> signal at 862 Hz. As this meter is a current source, it has a significantly higher impedance than the transformer magnetics, and thus does not require the capacitor shown in [3] to block the DC bias current.

The OCL of the transformer decreases with increased bias current. Thus, it is only necessary to test conformance with a bias current of 8 mA. The current source is realized using a DC voltage supply and a current mirror.

#### Test Setup: Refer to Appendix 25.A.

#### **Procedure:**

- 1. Turn the DUT off.

- 2. Adjust the DC current source until the bias current through the AOI is 8.0 mA.

- 3. Record the OCL as measured by the inductance meter.

**Observable Results:** The OCL at the AOI shall be at least 350 µH when measured with an 8 mA DC bias current.

#### **Possible Problems:**

The value of the OCL is known to have some temperature dependency. In order to account for this, it is suggested that the DUT to be powered for fifteen minutes before testing to allow it to reach an operating temperature.

Fast Ethernet Consortium

### Test #25.1.8 – Transmit Clock Frequency

Purpose: To verify that the frequency of the Transmit Clock is within the conformance limits

#### **References:**

- [1] IEEE Std 802.3u-1995, clause 25

- [2] Ibid., subclause 24.2.3.4, Timers

Resource Requirements: Refer to Appendix 25.A.

Last Modification: November 10, 2003 (Version 1.0)

#### **Discussion:**

Reference [1] describes the operation of the physical medium dependent (PMD) sublayer for 100Base-Tx devices. This clause incorporates ANSI X3.263-1995, by reference, with the exceptions listed in 25.4. Reference [2] defines the frequency of the fixed frequency oscillator for 100Base-Tx devices.

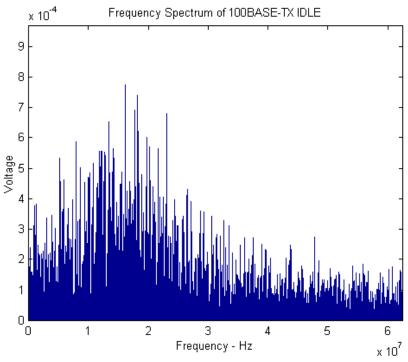

The reference clock used in this case is the recovered clock, which is the same one used during test 25.1.4, Transmit Jitter. After this clock has been recovered from the signal, its frequency is determined, and compared to a 125 MHz reference. The difference between the two is the deviation in the transmit clock.

The frequency of the recovered clock shall have a base frequency of 125 MHz  $\pm$  6.25 kHz.

Test Setup: Refer to Appendix 25.A.

#### **Procedure:**

- 1. Configure the DUT for 100BASE-TX operation. Ensure that the DUT is sending scrambled, MLT-3 encoded /I/ code-groups.

- 2. Measure the frequency of the clock derived from the transmitted IDLE signal and compare to 125 MHz.

- 3. For enhanced accuracy, repeat step 2 multiple times and average the frequencies measured.

**Observable Results:** The transmit clock generated by the DUT shall be 125 MHz  $\pm$  6.25 kHz

Possible Problems: None

## The University of New Hampshire InterOperability Laboratory GROUP 2: ACTIVE INPUT INTERFACE (AII)

### **Overview:**

This group of tests verifies the integrity of the Device Under Tests' Active Input Interface. This is done by using various frame reception and physical characterization tests.

### Scope:

All of the tests described in this section have been implemented and are currently active at the University of New Hampshire InterOperability Lab.

### **Test #25.2.1 – Differential Input Impedance**

**Purpose:** To verify that the return loss at the receiver of the device under test (DUT) is above the conformance limit.

#### **References:**

- [1] IEEE Std 802.3-2002, clause 25

- [2] ANSI X3.263-1995, section 9.2.2

- [3] Ibid., section 11.1.1

- [5] EIA/TIA TSB-36, section 4.2

Resource Requirements: Refer to Appendix 25.A

Last Modification: November 10, 2003 (Version 2.5)

#### **Discussion:**

Reference [1] describes the operation of the physical medium dependent (PMD) sublayer for 100Base-Tx devices. This clause incorporates ANSI X3.263-1995, by reference, with the exceptions listed in 25.4. Reference [2] defines the differential input impedance at the Active Input Interface (AII).

The differential input impedance is specified in terms of return loss which is a function of  $\Gamma$ , the reflection coefficient. The reflection coefficient is the ratio of the voltage in a wave reflected by a load,  $Z_L$ , to the voltage in the wave incident on that load. If the source of the incident wave has an impedance  $Z_S$ ,  $\Gamma$  is:

$$\Gamma = \frac{Z_{\rm L} - Z_{\rm S}}{Z_{\rm L} + Z_{\rm S}}$$

Since both  $Z_L$  and  $Z_S$  are complex numbers,  $\Gamma$  is complex. The return loss (RL) is the magnitude of  $\Gamma$  expressed in decibels:

$$\mathrm{RL}(\mathrm{dB}) = 20 \cdot \log_{10} \left| \frac{1}{\Gamma} \right|$$

Note that  $\Gamma$  is inverted to make the return loss greater than or equal to zero.

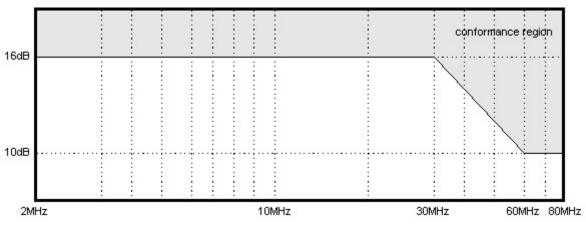

Figure 25.2.1-1: Return loss limit as a function of frequency.

The ANSI standard states that the differential input impedance shall be such that the return loss is above the limit line depicted in figure 25.2.1-1. The source impedance,  $Z_S$ , for the return loss measurement is defined to be the characteristic impedance of a twisted pair as specified in [3]. Reference [3] refers to EIA/TIA TSB-36 for the definition of category 5 unshielded twisted pair (UTP). Reference [4] states that the characteristic impedance shall be  $100\Omega \pm 15\%$ . Therefore, the return loss measurement is performed for both a  $Z_S$  of 85 $\Omega$  and a  $Z_S$  of 115 $\Omega$ .  $Z_S$  is assumed to be completely resistive.

#### Test Setup: Refer to Appendix 25.A.

#### **Procedure:**

- 1. Configure the DUT for 100BASE-TX operation.

- 2. Measure the impedance,  $Z_L$ , at the receiver in the frequency range of 2MHz to 80MHz.

- 3. Compute the return loss for a  $Z_S$  of 85 $\Omega$  and a  $Z_S$  of 115 $\Omega$ . Assume  $Z_S$  to be completely resistive.

Observable Results: The return loss at the AII shall not fall below the limit line depicted in figure 25.2.1-1.

#### **Possible Problems:**

In some cases, it is not possible to disable auto-crossover on the DUT. On these devices, the differential input impedance cannot be measured.

### **Test #25.2.2 – Adaptive Equalization**

**Purpose:** To verify that, under worst-case operating conditions, the device under test (DUT) correctly compensates for the wide range of attenuation and phase distortion introduced by cable.

#### **References:**

- [1] IEEE Std. 802.3-2002, clause 25

- [2] ANSI X3.263-1995, section 9.2.1

- [3] Ibid., Annex A, section A.1

- [4] TIA/EIA-568-A-1995, Annex E (informative)

#### Resource Requirements: Refer to Appendix 25.A

**Last Modification:** November 10, 2003 (Version 1.1)

#### **Discussion:**

Reference [1] describes the operation of the physical medium dependent (PMD) sublayer for 100Base-Tx devices. This clause incorporates ANSI X3.263-1995, by reference, with the exceptions listed in 25.4. Reference [2] defines a set of differential input signals that must be accepted by the Active Input Interface (AII).

The differential input signals are defined to be the outputs of the test channels defined in [3]. Each test channel is driven by a differential transmitter that meets or exceeds the specifications of the section 9.1 (Active Output Interface). Five test channels are defined that represent 5, 25, 50, 75, and 100% of the maximum attenuation expected in the application environment. The NEXT loss of each test channel is defined to keep the attenuation-to-crosstalk ratio consistent among the channels.

The intention of the five test channels is to ensure that the AII correctly compensates for the wide range of attenuation and phase distortion introduced by cable. This test expands upon the differential input signals concept and addresses the problems with the specified test channels and methodology.

The first problem lies in the test channel definitions. The application environment for 100BASE-TX is expected to be category 5 cable installed according to TIA/EIA-568-A. However, a compliant TIA installation could have higher attenuation than what is represented in the worst-case test channel. The difference is due to the following factors:

- a. The worst-case test channel assumes 3 category 5 connectors while TIA/EIA-568-A allows up to 4. It is interesting to note that section 11.1.8 of ANSI X3.263 also states that the channel may contain up to 4 connectors which conflicts with the worst-case channel definition given in the same standard.

- b. The worst-case test channel assumes a 0.3% increase in attenuation per degree Celsius above room temperature (20°C). TIA/EIA-568-A allows up to 0.4% per degree Celsius.

This test steps the attenuation from 5% to 100% of the worst-case TIA/EIA-568-A attenuation in 5% increments. Note that this test does not attempt to maintain a consistent attenuation-to-crosstalk ratio. The NEXT loss of each channel is set to the worst-case NEXT loss allowed by TIA.

The second problem is that the target bit error rate for the AII is not specified. The intention of this test is to find what levels of attenuation, if any, result in severe under- or over-equalization. Since such failures are expected to result in high error rates, this test will attempt to prove that the BER is greater than  $10^{-8}$  for each iteration. Based on the analysis given in appendix 25.D, if more than 7 errors are observed in  $3\times10^{8}$  bits (about 470,000 64-byte packets), it can be concluded that the error rate is greater than  $10^{-8}$  with less than a 5% chance of error. Note that if no errors are observed, it can be concluded that the BER is no more than  $10^{-8}$  with less than a 5% chance of error.

This test is repeated for transmitter response times of 3 and 5ns. A response time of 3ns maximizes the signal bandwidth while a response time of 5ns results in the worst-case quantization error for digital implementations.

Table 25.2.2-1 summarizes the model parameters used in this test in the context of the link model defined in appendix 25.C.

| Parameter        | Description                         | Value                       | Units                             |

|------------------|-------------------------------------|-----------------------------|-----------------------------------|

| $J_{pp}$         | Peak-peak jitter                    | 1.4                         | ns                                |

| t <sub>r</sub>   | Response time                       | 3 (5)                       | ns                                |

| %OS              | Waveform overshoot                  | 5                           | %                                 |

| R <sub>s</sub>   | Transmitter source impedance        | 100                         | Ω                                 |

| R <sub>L</sub>   | Receiver load impedance             | 100                         | Ω                                 |

| $L_1$            | Transmitter open circuit inductance | 350                         | μH                                |

| $L_2$            | Receiver open circuit inductance    | 350                         | μH                                |

| R <sub>WG</sub>  | Waveform generator source impedance | 100                         | Ω                                 |

| R <sub>DUT</sub> | DUT load impedance                  | 100                         | Ω                                 |

| L <sub>DUT</sub> | DUT open circuit inductance         | measured in test #25.1.7    | μH                                |

| 1                | Cable length                        | 5 to 100 in increments of 5 | m                                 |

| Т                | Temperature                         | 60                          | °C                                |

| V <sub>out</sub> | Differential output voltage         | 950                         | mV                                |

| С                | Number of connectors in the channel | 4                           |                                   |

| М                | Flat loss margin                    | 0.3                         | dB                                |

| N <sub>B</sub>   | Reference NEXT loss (at 16MHz)      | 40.5                        | dB                                |

| N <sub>M</sub>   | NEXT loss scale                     | 16.6                        | <sup>dB</sup> / <sub>decade</sub> |

Table 25.2.2-1: Summary of model parameters for test #25.2.2

Test Setup: Refer to Appendix 25.A.

#### **Procedure:**

- 1. Configure the link simulator to use the model parameters in table 25.2.2-1 with a response time of 3ns and cable length of 5m. The link simulator will send 500,000 64-byte packets and the monitor will count the number of packet errors.

- 2. Repeat step 1, incrementing the cable length by 5m with each iteration, until the cable length reaches 100m.

- 3. Repeats steps 1 and 2 for a response time of 5ns.

**Observable Results:** There shall be no more than 7 errors for any iteration.

#### **Possible Problems:**

The rate at which the device under test can process incoming packets may make the test duration prohibitive. In such cases, fewer packets may be sent resulting in a lower confidence that a bit error rate of  $10^{-8}$  is being met.

### **Test #25.2.3 – Baseline Wander Correction**

Purpose: To verify that the device under test (DUT) can correct worst-case baseline wander events.

#### **References:**

- [1] IEEE Std. 802.3-2002, clause 25

- [2] ANSI X3.263-1995, section 9.2.1

- [3] Ibid., Annex A, section A.1

- [4] Ibid., Annex A, section A.2

- [5] TIA/EIA-568-A-1995, Annex E (informative)

#### **Resource Requirements:** Refer to Appendix 25.A

**Last Modification:** November 10, 2003 (Version 1.1)

#### **Discussion:**

The operation of the 100BASE-TX PMD sublayer is defined in [1]. Clause 25 incorporates ANSI X3.263 by reference with the exceptions listed in subclause 25.4. Reference [2] defines a set of differential input signals that must be accepted by the Active Input Interface (AII).

The differential input signals specification is intended to ensure that the AII correctly compensates for the wide range of attenuation and phase distortion introduced by cable. The test expands upon the differential input signals concept by verifying that the AII also corrects worst-case baseline wander events.

As the baseline wander model in appendix 25.C shows, the order of the channel's low frequency response is a function of cable length. The channel response is first-order highpass for a cable length of zero and secondorder highpass for cable lengths greater than zero. This test applies the extreme cases of 0m and 100m cable lengths.

For each cable length, two baseline wander patterns are applied to the AII. Note that these patterns will generate the worst-case baseline wander event if, at the first bit of the pattern, the scrambler seed is 390 and the MLT-3 output symbol is 0.

- Test Pattern #1: This pattern is given in annex A, section A.2 of ANSI X3.263 but has been truncated to fit in a 1,518-byte packet. It creates a worst-case unidirectional baseline wander event.

- Test Pattern #2: This is a modified version of test pattern 1 which has been altered to flip the polarity of the baseline wander at one-quarter and three-quarters of the pattern length. This creates the worst-case bi-directional baseline wander event.

There is no specification for the bit error rate that the AII is expected to maintain in the presence of worstcase baseline wander events. It is expected that incorrect compensation will result in a high error rate and that a rigorous BER measurement is not required. This test will attempt to prove that the BER is greater than  $10^{-8}$  for each iteration. Based on the analysis given in appendix 25.D, if more than 7 errors are observed in  $3\times10^{8}$  bits (about 20,000 1518-byte packets), it can be concluded that the error rate is greater than  $10^{-8}$  with less than a 5% chance of error. Note that if no errors are observed, it can be concluded that the BER is no more than  $10^{-8}$  with less than a 5% chance of error.

Fast Ethernet Consortium

Each test is repeated for transmitter response times of 3 and 5ns. A response time of 3ns maximizes the signal bandwidth while a response time of 5ns results in the worst-case quantization error for digital implementations.

Table 25.2.3-1 summarizes the model parameters used in this test in the context of the link model defined in appendix 25.C.

| Parameter        | Description                         | 1 <sup>st</sup> Order | 2 <sup>nd</sup> Order | Units                             |

|------------------|-------------------------------------|-----------------------|-----------------------|-----------------------------------|

| J <sub>pp</sub>  | Peak-peak jitter                    | 1.4                   | 1.4                   | ns                                |

| t <sub>r</sub>   | Response time                       | 3 (5)                 | 3 (5)                 | ns                                |

| %OS              | Waveform overshoot                  | 5                     | 5                     | %                                 |

| R <sub>s</sub>   | Transmitter source impedance        | 100                   | 100                   | Ω                                 |

| R <sub>L</sub>   | Receiver load impedance             | 100                   | 100                   | Ω                                 |

| $L_1$            | Transmitter open circuit inductance | 350                   | 350                   | μH                                |

| $L_2$            | Receiver open circuit inductance    | 350                   | 350                   | μH                                |

| R <sub>WG</sub>  | Waveform generator source impedance | 100                   | 100                   | Ω                                 |

| R <sub>DUT</sub> | DUT load impedance                  | 100                   | 100                   | Ω                                 |

| L <sub>DUT</sub> | DUT open circuit inductance         | measured in           | test #25.1.7          | μH                                |

| 1                | Cable length                        | 0                     | 100                   | m                                 |

| Т                | Temperature                         | 60                    | 60                    | °C                                |

| V <sub>out</sub> | Differential output voltage         | 950                   | 950                   | mV                                |

| С                | Number of connectors in the channel | 0                     | 4                     |                                   |

| М                | Flat loss margin                    | 0.3                   | 0.3                   | dB                                |

| N <sub>B</sub>   | Reference NEXT loss (at 16MHz)      | 40.5                  | 40.5                  | dB                                |

| N <sub>M</sub>   | NEXT loss scale                     | 16.6                  | 16.6                  | <sup>dB</sup> / <sub>decade</sub> |

Table 25.2.3-1: Summary of model parameters for first and second order high-pass responses.

Test Setup: Refer to Appendix 25.A.

#### **Procedure:**

- 1. Configure the link simulator to use the model parameters given in table 25.2.3-1 (1<sup>st</sup> order column) with a response time of 3ns.

- 2. The link simulator will send 20,000 1,518-byte packets containing test pattern #1. The monitor will count the number of packet errors.

- 3. The link simulator will send 20,000 1,518-byte packets containing test pattern #2. The monitor will count the number of packet errors.

- 4. Repeat steps 1 through 3 after configuring the link simulator to use the model parameters given in table 25.2.3-1 (2<sup>nd</sup> order column) with a response time of 3ns.

- 5. Repeat steps 1 through 4 with a response time of 5ns.

Observable Results: There shall be no more than 7 errors for any iteration.

#### **Possible Problems:**

The rate at which the device under test can process incoming packets may make the test duration prohibitive. In such cases, fewer packets may be sent resulting in a lower confidence that a bit error rate of  $10^{-8}$  is being met.

### **Test #25.2.4 – Bit Error Rate Verification**

**Purpose:** To verify that the device under test (DUT) can maintain low bit error rate even in the presence of the worst-case input signal-to-noise ratio.

#### **References:**

- [1] IEEE Std. 802.3-2002, clause 25

- [2] ANSI X3.263-1995, section 9.2.1

- [3] Ibid., Annex A, section A.1

- [4] TIA/EIA-568-A-1995, Annex E (informative)

Resource Requirements: Refer to Appendix 25.A

**Last Modification:** November 10, 2003 (Version 1.1)

#### **Discussion:**

The operation of the 100BASE-TX PMD sublayer is defined in [1]. Clause 25 incorporates ANSI X3.263 by reference with the exceptions listed subclause 25.4. Reference [2] defines a set of differential input signals that must be accepted by the Active Input Interface (AII).

The differential input signals specification is intended to ensure that the AII correctly compensates for the wide range of attenuation and phase distortion introduced by cable. While test 25.2.2 performs a thorough evaluation of the adaptive equalizer circuit, it only verifies a relatively high bit error rate. This test attempts to verify a much lower bit error rate in the presence of poor signal-to-noise ratio. Specifically, the bit error rate is verified for cable lengths of 75 and 100m.

Note that the bit error rate target for 100BASE-TX is not specified in either IEEE Std. 802.3-2002 or ANSI X3.263. This test will attempt to prove that the BER is greater than  $10^{-11}$  for each iteration. Based on the analysis given in appendix 25.D, if more than 7 errors are observed in  $3x10^{11}$  bits (about 19,770,000 1,518-byte packets), it can be concluded that the error rate is greater than  $10^{-11}$  with less than a 5% chance of error. Note that if no errors are observed, it can be concluded that the BER is no more than  $10^{-11}$  with less than a 5% chance of error.

This test is repeated for transmitter response times of 3 and 5ns. A response time of 3ns maximizes the signal bandwidth while a response time of 5ns results in the worst-case quantization error for digital implementations.

Table 25.2.4-1 summarizes the model parameters used in this test in the context of the link model defined in appendix 25.C.

| Parameter        | Description                         | Value                    | Units                             |

|------------------|-------------------------------------|--------------------------|-----------------------------------|

| $J_{pp}$         | Peak-peak jitter                    | 1.4                      | ns                                |

| t <sub>r</sub>   | Response time                       | 3 (5)                    | ns                                |

| %OS              | Waveform overshoot                  | 5                        | %                                 |

| R <sub>s</sub>   | Transmitter source impedance        | 100                      | Ω                                 |

| R <sub>L</sub>   | Receiver load impedance             | 100                      | Ω                                 |

| $L_1$            | Transmitter open circuit inductance | 350                      | μH                                |

| $L_2$            | Receiver open circuit inductance    | 350                      | μH                                |

| R <sub>WG</sub>  | Waveform generator source impedance | 100                      | Ω                                 |

| R <sub>DUT</sub> | DUT load impedance                  | 100                      | Ω                                 |

| L <sub>DUT</sub> | DUT open circuit inductance         | measured in test #25.1.7 | μH                                |

| 1                | Cable length                        | 75 and 100               | m                                 |

| Т                | Temperature                         | 60                       | °C                                |

| V <sub>out</sub> | Differential output voltage         | 950                      | mV                                |

| С                | Number of connectors in the channel | 4                        |                                   |

| М                | Flat loss margin                    | 0.3                      | dB                                |

| N <sub>B</sub>   | Reference NEXT loss (at 16MHz)      | 40.5                     | dB                                |

| N <sub>M</sub>   | NEXT loss scale                     | 16.6                     | <sup>dB</sup> / <sub>decade</sub> |

### Table 25.2.4-1: Summary of model parameters for test #25.2.4

Test Setup: Refer to Appendix 25.A.

#### **Procedure:**

- 1. Configure the link simulator to use the model parameters defined in table 25.2.4-1 with a response time of 3ns and a cable length of 75m.

- 2. The link simulator shall send 20,000,000 1,518-byte packets and the monitor will count the number of packet errors.

- 3. Repeat steps 1 and 2 for a cable length of 100m.

- 4. Repeat steps 1 through 3 for a response time of 5ns.

**Observable Results:** There shall be no more than 7 errors for any iteration.

#### **Possible Problems:**

The rate at which the device under test can process incoming packets may make the test duration prohibitive. In such cases, fewer packets may be sent resulting in a lower confidence that a bit error rate of  $10^{-11}$  is being met.

## The University of New Hampshire InterOperability Laboratory TEST SUITE APPENDICES

### **Overview:**

The appendices contained in this section are intended to provide additional low-level technical details pertinent to specific tests defined in this test suite. Test suite appendices often cover topics that are beyond the scope of the standard, but are specific to the methodologies used for performing the measurements covered in this test suite. This may also include details regarding a specific interpretation of the standard (for the purposes of this test suite), in cases where a specification may appear unclear or otherwise open to multiple interpretations.

### Scope:

Test suite appendices are considered informative, and pertain only to tests contained in this test suite.

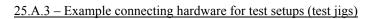

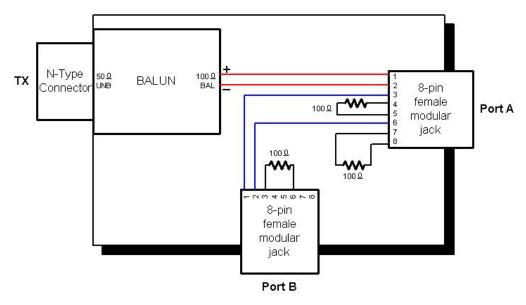

### **Appendix 25.A – Test Setup Implementation Examples**

**Purpose:** To present an example of the test setups and connecting hardware that may be used to implement the 100BASE-TX PMD test suite.

#### **References:**

- [1] IEEE Std 802.3-2002, clause 25

- [2] ANSI X3.263-1995, section 9.1

#### **Resource Requirements:**

- Digital storage oscilloscope, Tektronix TDS7104 or equivalent

- Vector Network Analyzer, HP 8753C or equivalent

- Test Jigs #1, #2, #3

- 100Base-Tx Idle Source

- DC Power Supply (1A)

- DC Current Meter

- Inductance Meter

- Disturbing signal generator, Tektronix AWG2041 or equivalent

- Netcom Systems Smartbits

- Controlling software (MATLAB)

**Last Modification:** November 10, 2003 (Version 1.1)

#### **Discussion:**

#### 25.A.1 – Introduction

This appendix describes of the implementation of the 100BASE-TX PMD test suite used by the University of New Hampshire. This description is intended to be an example for those that wish to implement the test suite in their own lab.

Note that in the cases where specific equipment models are specified, any piece of equipment with similar capabilities may be substituted. Also note that the length of the unshielded twisted pair (UTP) cable used to connect the device under test (DUT) to the test jig should be kept as short as possible (less than a foot). If longer lengths are necessary, the impact of the cable on the measurement must be evaluated and steps taken to remove its effect.

### 25.A-2 – Test Setup Examples

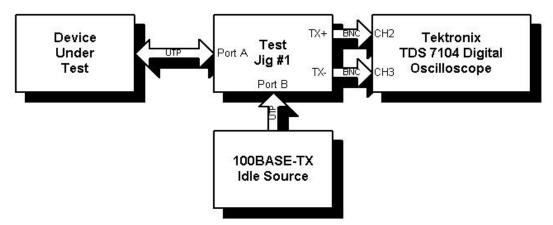

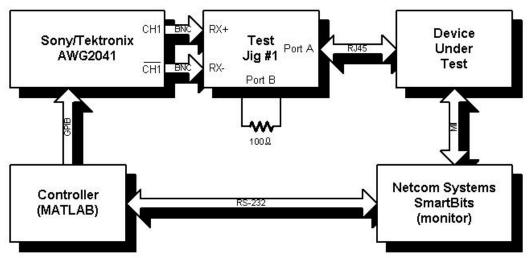

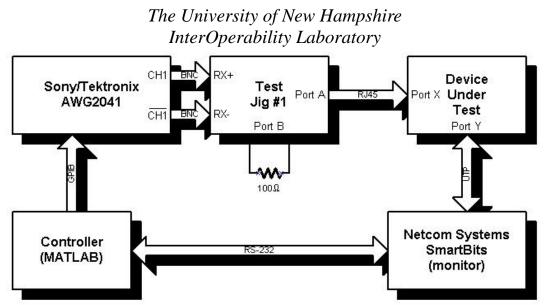

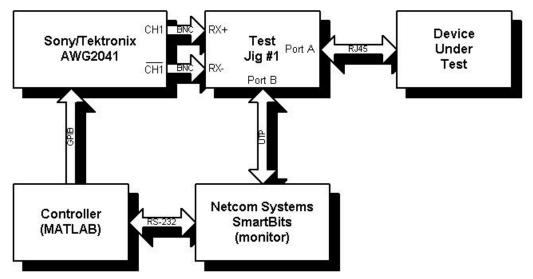

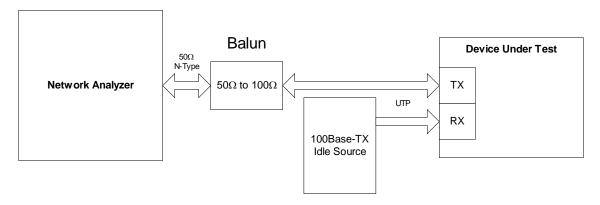

Figure 25.A-1: Example test setup for tests 25.1.1 through 25.1.5 (pulse parameters and transmit jitter).

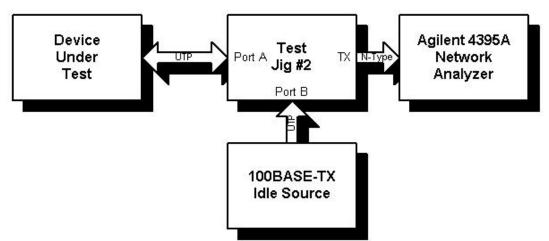

Figure 25.A-2: Example test setup for tests 25.1.6 and 25.2.1 (return loss).

Fast Ethernet Consortium

Figure 25.A-3: Example test setup for test 25.1.7 (transmitter open circuit inductance).

Figure 25.A-4: Example test setup for tests 25.2.2 through 25.2.4 (Active Input Interface tests, DUT is an MII transceiver).

Figure 25.A-5: Example test setup for tests 25.2.2 through 25.2.4 (Active Input Interface tests, DUT is a repeater, switch, router or other packet forwarding device).

Figure 25.A-6: Example test setup for tests 25.2.2 through 25.2.4 (Active Input Interface tests, DUT is a workstation or other single port device).

Figure 25.A-7: Test jig #1

Figure 25.A-8: Test jig #2

## Appendix 25.B – Transmit Jitter Measurement

**Purpose:** To present a method of jitter measurement that does not require access to the transmit clock.

## **References:**

- [1] IEEE Std. 802.3-2002, subclause 24.2.3.4 Physical Coding Sublayer (PCS) and Physical Medium Attachment (PMA) Sublayer, type 100BASE-X, Timers.

- [2] IEEE Std. 802.3-2002, clause 25 Physical Medium Dependent (PMD) sublayer and baseband medium, type 100BASE-TX.

- [3] ANSI X3.263-1995, section 9.1.9 Jitter.

- [4] T11.2/Project 1230/Revision 7.0 Methodology for Jitter Specification.

**Last Modification:** February 15, 1999 (Version 1.0)

### **Discussion:**

#### 25.B.1 – Introduction

Jitter is the difference between the time that an event was expected to occur and the time that the event actually occurred. In the context of a digital communications link, jitter is the offset between the expected position of a signal transition and the actual position of the transition. The magnitude of these offsets must be limited in order to limit the chances of an error on the link.

To measure jitter, the expected position of the signal transition must be known. The reference clock provides an indication of where a transition is supposed to occur. In a typical jitter measurement, the clock input to the transceiver under test is used as the reference clock. However, this signal is not always available. This appendix presents a reliable method of jitter measurement that derives the reference clock directly from the MLT-3 symbol sequence.

## 25.B.2 – Transmit Jitter Model

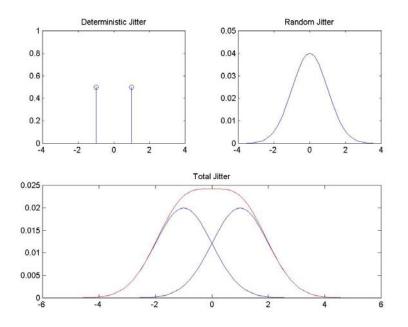

Jitter can be thought of as phase modulation of the MLT-3 symbol sequence. The modulation function has independent deterministic and random components. Deterministic jitter is attributed to inter-symbol interference (ISI), duty cycle distortion, and sinusoidal frequency modulation. ISI describes the pulse distortions caused by the bandwidth limitations of the system. The distortion is a function of the pulses that precede and follow pulse of interest and thus is often referred to as data-dependent jitter (DDJ).

Duty cycle distortion (DCD), as measured in test 25.1.3, is peak-to-peak deviation of the measured symbol interval from its expected value. While all jitter components alter the measured symbol interval, DCD is a static deviation that is a function of difference between the propagation of signal rise and fall. The distribution of DDJ is influenced by DCD.

Further modulation of the baseband signal is caused by the coupling of sinusoidal signals into the phaselocked loop circuit. Usually this modulation is from low frequency signals that sneak in through the power supply. Since there is no clear relationship between this form of jitter and the MLT-3 symbol sequence, it is typically referred to as uncorrelated deterministic jitter (UDJ).

Random jitter is modeled as white noise. An offset whose amplitude is picked from a zero-mean normal distribution is applied to each signal transition. The offsets are assumed to be independent, that is, the amplitude of the current offset is not influenced by the amplitudes of the preceding or following offsets. Random jitter is typically characterized by the standard deviation of the distribution from which the amplitudes are drawn. Note that a peak-to-peak value for the random jitter cannot be computed without first setting the probability that the given

value will be exceeded. Given that probability, the peak-to-peak random jitter is a function of the standard deviation.

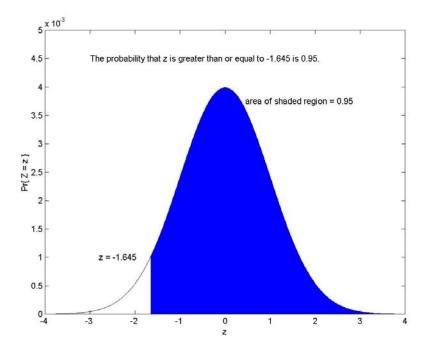

Given the probabilistic nature of random jitter, it is useful to also model deterministic jitter with a distribution function. The total jitter distribution then becomes the convolution of the deterministic and random distributions. This concept is illustrated in figure 25.B-1.

Figure 25.B-1: The total jitter distribution is the convolution of the deterministic and random distributions.

The measurement technique presented in this appendix assumes that the dominant contributions to the deterministic jitter are data-dependent jitter and duty cycle distortion. This implies that for a repeating sequence of N MLT-3 symbols, there can be no more than N distinct values for the deterministic jitter. Since the random jitter distribution is assumed to be zero-mean, the deterministic jitter value for a given signal transition is the mean jitter observed in that transition. The deterministic jitter distribution is simply a histogram of the N deterministic jitter values.

## 25.B.3 – Derivation of Reference Clock

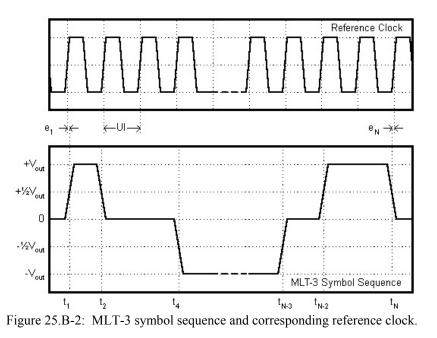

The reference clock indicates where a signal transition is supposed to occur. The period of the reference clock is referred to as the unit interval (UI) and it is the duration of one MLT-3 symbol. This measurement technique derives the unit interval directly from the symbol sequence. The derivation assumes that the UI is constant over the interval of estimation.

Refer to figure 25.B-2. Let  $t_n$  be the time a signal transition crosses 50% of the differential output voltage,  $V_{out}$ . If  $t_1$  is the position of the first signal transition, then the subscript n can be computed using equation 25.B-1.

$$n = \operatorname{round}\left(\frac{t_n - t_1}{8\mathrm{ns}}\right)$$

(Equation 25.B-1)

Note that 8ns is the nominal unit interval. Equation 25.B-1 is incorrect if  $(t_n-t_1)/(n-1)$  differs from the nominal unit interval by more than 4ns. Such a difference is caused by deviation of the actual unit interval from the

nominal value and the difference between the jitter in the first and n<sup>th</sup> transitions. The actual UI of a conformant device will not deviate from the nominal value by more than 0.005%. Assuming that the difference between the jitter in the first and n<sup>th</sup> transitions is less than 1.4ns, the worst-case UI will make equation 25.B-1 invalid for n less than 6,500.

Let N be the last signal transition in the record. Assuming that N is less than 6,500, the difference between the positions of the first and N<sup>th</sup> transitions is given as equation 25.B-2.

$$t_N - t_1 = (N - 1)UI + e_N - e_1$$

(Equation 25.B-2)

Divide equation 25.B-2 by (N-1) to produce equation 25.B-3.

$$\frac{t_N - t_1}{N - 1} = UI + \frac{e_N - e_1}{N - 1}$$

(Equation 25.B-3)

Thus, we have produced an estimate of the unit interval whose error is proportional to the difference between the jitter in the first and N<sup>th</sup> transitions. The estimate is formally stated in equation 25.B-4.

$$UI_{est} = \frac{t_N - t_1}{N - 1} = UI + \frac{e_N - e_1}{N - 1}$$

(Equation 25.B-4)

## 25.B.4 – Computation of the Timing Error

An estimate of the time offset at each signal transition,  $e_{n,est}$ , is given in equation 25.B-5.

$$e_{n est} = t_n - (n-1)UI_{est}$$

Substituting equation 25.B-4 into equation 25.B-5 gives us equation 25.B-6.

(Equation 25.B-5)

$$e_{n,est} = t_n - (n-1)UI - (n-1)\frac{e_N - e_1}{N-1}$$

Manipulating equation 25.B-3 and making is applicable to all n, we produce equation 25.B-7.

$$t_n - (n-1)UI = t_1 + e_n - e_1$$

(Equation 25.B-7)

Substituting back into equation 25.B-6 gives us equation 25.B-8.

$$e_{n,est} = t_1 + e_n - e_1 - (n-1)\frac{e_N - e_1}{N-1}$$

(Equation 25.B-8)

Thus, the estimate of the jitter in the n<sup>th</sup> signal transition contains an error term that is a linear function of n. Figure 25.B-3 shows  $e_{n,est}$  as a function of n. In the figure, the error slope  $(e_N-e_1)/(N-1)$  is labeled m and the error intercept  $(t_1-e_1)$  is labeled b.

The slope and intercept of the error term are functions of the unknowns  $e_1$  and  $e_N$ . Assuming that the total jitter distribution has a mean value of zero, m and b may be found by performing a least squares line fit to the estimated jitter. Given m and b, the actual jitter in the nth transition can be computed using equation 25.B-9.

$$e_n = e_{n,est} - b + (n-1)m$$

25.B.5 - Jitter Statistics

For each value of n, the mean and standard deviation of the jitter are estimated. The mean is the value of the deterministic jitter for that signal transition. The standard deviation completely characterizes the random jitter for that transition. If K samples of  $e_n$  are taken, the mean value of  $e_n$  can be estimated using equation 25.B-10.

40

b e<sub>N-2,est</sub> e<sub>N</sub> 1 2 3 4 N-3 N-2 N-1 Ν Figure 25.B-3: Estimated jitter as a function of n.

Clause 25 PMD Test Suite v3.2

(Equation 25.B-9)

(Equation 25.B-10)

(Equation 25.B-6)

$$s_n^2 = \frac{1}{(K-1)} \sum_{k=1}^{K} (e_{n,k} - m_n)^2$$

(Equation 25.B-11)

#### 25.B.6 - Computation of Total Transmit Jitter

The reference pattern for the transmit jitter measurement is scrambled, MLT-3 encoded, /I/ code-groups. This pattern repeats once every 8,188 symbols and it contains 4,092 signal transitions. This implies that there are no more than 4,092 distinct values for data-dependent jitter. It has been assumed that data-dependent jitter and duty cycle distortion are the dominant contributors to deterministic jitter. If this is the case, then there are no more than 4,092 distinct values for deterministic jitter.

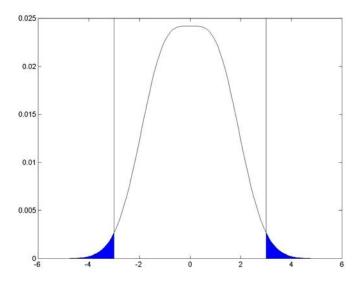

Thus, a deterministic jitter distribution can be constructed by measuring the mean at each of the MLT-3 transitions in the pattern and building a histogram. The total jitter distribution is the convolution of this histogram and a zero-mean normal distribution function. The standard deviation of the normal distribution is the value estimated from one of the signal transitions.

Since the jitter has a random component, a peak-to-peak total jitter value cannot be computed without specifying the probability that the value will be exceeded. Referring to figure 25.B-4, the probability that a given peak-to-peak value will be exceeded is the area under the tails of the distribution (the shaded regions).

Figure 25.B-4: Peak-to-peak total jitter.

## Appendix 25.C – Link Model

Purpose: To define comprehensive models of the TP-PMD transmitter and channel.

### **References:**

- [1] ANSI X3.263-1995, section 9.1.7 Worst Case Droop of Transformer.

- [2] Ibid., section 9.1.10 Characteristics of Active Output Interface.

- [3] Ibid., section 11.1.2 Insertion Loss Definitions.

- [4] Ibid., section 11.1.3 Crosstalk Definitions.

- [5] Ibid., section 11.1.4 Reference Insertion Loss and Reference Crosstalk Attenuation Values.

- [6] Ibid., Annex A.1 (normative) Test channel requirements (twisted pair model)

- [7] ANSI/TIA/EIA-568-A-1995, section 10.2.4.1 DC Resistance (Horizontal UTP Cable).

- [8] Ibid., section 10.2.4.6 Attenuation (Horizontal UTP Cable).

- [9] Ibid., section 10.2.4.7 Near End Crosstalk (NEXT) Loss (Horizontal UTP Cable).

- [10] Ibid., section 10.4.4.1 Attenuation (Connecting Hardware for UTP Cable).

- [11] Ibid., section 10.4.4.2 NEXT Loss (Connection Hardware for UTP Cable).

- [12] Ibid., section 10.5.4.1 Attenuation (UTP Patch Cords and Cross-Connect Jumpers).

- [13] Ibid., Annex E (informative) UTP Channel Performance.

Last Modification: January 28, 1999 (Version 1.0)

### **Discussion:**

### 25.C.1 – Introduction

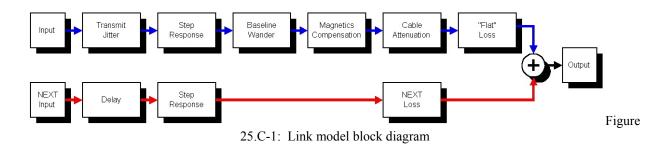

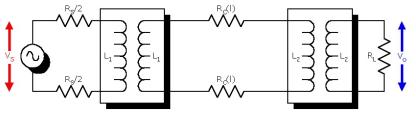

Figure 25.C-1 shows a block diagram of the link model used in test #25.2.2 - Adaptive Equalization, test #25.2.3 - Baseline Wander Compensation, and test #25.2.4 - Bit Error Rate Verification. Each component of the block diagram is described below.

## 25.C.2 - Transmit Jitter

The transmit jitter model applies a random timing offset to each MLT-3 transition. The amplitude of the offset is chosen from zero-mean uniform probability distribution function. While jitter is typically modeled with a normal distribution function, this model uses a uniform distribution so that larger amplitudes are chosen more frequently.

A sequence of numbers,  $\mathbf{x}$ , produced by a uniform random number generator can be converted to a sequence of suitable timing offsets,  $\mathbf{e}$ , using equation 25.C-1.

$$\mathbf{e} = J_{pp} \frac{\mathbf{x} - \text{mean}(\mathbf{x})}{\text{max}(\mathbf{x}) - \text{min}(\mathbf{x})}$$

(Equation 25.C-1)

Equation 25.C-1 guarantees that the transmit jitter will have zero mean and a peak-peak value of  $J_{pp}$ . Note that  $J_{pp}$  is specified to be less than 1.4ns [2].

#### <u>25.C.3 – Transmitter Step Response</u>

The step response of an MLT-3 line driver is modeled as a second-order lowpass filter. The transfer function of this filter is given in equation 25.C-2.

$$H_{lp} = \frac{\omega_n^2}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

(Equation 25.C-2)

Note that s is shorthand for  $j2\pi f$  where j is the square root of -1 and f is frequency in Hertz. The parameter  $\zeta$  is referred to as the damping ratio and is related to the percent overshoot of the step response. The relationship is given in equation 25.C-3.

$$%OS = \exp\left(-\pi \frac{\zeta}{\sqrt{1-\zeta^2}}\right)$$

(Equation 25.C-3)

There is no precise analytical relationship between  $\zeta$  and the response time,  $t_r$ . However, for a given  $\zeta$ , there is a relationship between  $t_r$  and  $\omega_n$ . To understand this relationship, consider the filter's step response (underdamped case) given in equation 25.C-4.

$$h_{lp}(t) = 1 - Ce^{-\zeta \omega_n t} \cos\left(\frac{\omega_n t}{C} + \varphi\right)$$

$$C = \frac{1}{\sqrt{1 - \zeta^2}}$$

$$\varphi = \tan^{-1}(C\zeta)$$

(Equation 25.C-4)

Recall that the response time is the time difference between the points where the step crosses 10% and 90% of its steady state voltage. Given  $\zeta$ , iterative methods can be used to solve  $h_{lp}(t) = 0.1$  and  $h_{lp}(t) = 0.9$  for  $\omega_n t$ . The difference between these two solutions is  $\omega_n t_r$  from which  $\omega_n$  can be easily derived for a given  $t_r$ .

Note that the waveform overshoot is specified to be less than 5% and the response time is specified to be between 3 and 5ns [2].

### 25.C.4 – Baseline Wander

The baseline wander model is intended to duplicate the DC rejection properties of the channel. The low frequency response is determined by the magnetics at the transmitter, the cable, and the magnetics at the receiver. This model assumes that the frequencies being considered are low enough to model the cable as a lumped

resistance. This model also assumes that the magnetics at the transmitter and receiver are both ideal transformers with ideal coupling and a 1:1 turns ratio. The equivalent circuit of the channel is given in figure 25.C-2.

Figure 25.C-2: Baseline wander circuit model

The tran sfer function  $V_o/V_s$  is given in equation 25.C-5.

$$H_{hp}(s) = \frac{V_o}{V_s} = \frac{b_2 s^2}{a_2 s^2 + a_1 s + a_0}$$

$$b_2 = L_1 L_2 R_L$$

$$a_2 = L_1 L_2 (R_s + 2R_C R_L)$$

$$a_1 = R_s R_L (L_1 + L_2) + 2R_C (R_s L_2 + L_1 R_s)$$

$$a_0 = 2R_C R_s R_L$$

(Equation 25.C-5)

Note that the transfer function is a second-order highpass filter. The parameter  $R_c$ , which is the resistance of each conductor in the twisted pair wire, is a function of the cable length, l.  $R_c$  is specified to be no more than 9.38 $\Omega$  per conductor for 100m of cable at 20°C [7]. Assuming a linear increase in  $R_c$  per unit length,  $R_c$  is given in equation 25.C-6.

$$R_C = 0.0938 \cdot l \tag{Equation 25.C-6}$$

It is also assumed that  $R_C$  will increase 0.4% per degree Celsius above 20°C. Note that as the length of the cable approaches zero,  $R_C$  also approaches zero. As  $R_C$  approaches zero, the transfer function approaches a first-order highpass response. This transfer function is given in equation 25.C-7.

$$H_{hp}(s)\Big|_{R_{c}=0} = \frac{sL_{1}L_{2}R_{L}}{sL_{1}L_{2}(R_{S}+R_{L})+R_{S}R_{L}(L_{1}+L_{2})}$$

(Equation 25.C-7)

Note that the self inductance of the transformer coils, L1 and L2, is specified to be at least 350µH [1].

#### 25.C.5 - DUT Magnetics Compensation

ı.

The baseline wander model includes the receive magnetics and line termination. However, these components are also embedded in the device under test (DUT). To eliminate this duplicity, a filter is constructed that compensates for the magnetics in the DUT and allows the baseline wander model to completely define the channel's low frequency response.

Consider the typical test configuration in which a waveform generator is connected to the DUT. An equivalent circuit for this configuration is shown in figure 25.C-3.

Figure 25.C-3: Test setup equivalent circuit.

The magnetics compensation filter is defined by the transfer function  $V_s/V_o$  which is given in equation 25.C-8.

$$H_{DUT}(s) = \frac{V_S}{V_o} = \frac{sL_{DUT}(R_{DUT} + R_{WG}) + R_{DUT}R_{WG}}{sL_{DUT}R_{DUT}}$$

(Equation 25.C-8)

### 25.C.6 - Cable Attenuation

Cable attenuation is typically assumed to be a pure "skin effect" loss. The skin effect describes the tendency of AC currents to ride along the surface of a conductor. Higher frequencies correspond to a thinner skin and a higher loss. The transfer function of a pure skin effect loss is given in equation 25.C-9.

$$H_{skin}(s) = \frac{V_o}{V_i} = e^{-kl\sqrt{f}} e^{-jkl\sqrt{f}}$$

(Equation 25.C-9)

In equation 25.C-9, 1 denotes the length of the cable in meters, f is the frequency in Hertz, and k is a constant that will be derived from the standard for category 5 cable. The upper bound on attenuation in decibels for 100m of category 5 cable at 20°C is given in equation 25.C-10 [8].

Attenuation(f) =

$$1.967 \times 10^{-3} \cdot \sqrt{f} + 2.3 \times 10^{-8} \cdot f + \frac{5 \times 10^{-3}}{\sqrt{f}}$$

(Equation 25.C-10)

Equation 25.C-10 is valid for frequencies in the range of 0.772 to 100MHz. Note that this expression is a skin effect loss,  $f^{1/2}$ , with two correction terms. The linear term is a high frequency correction that has a significant impact on the cable attenuation (i.e. greater than 2dB at 100MHz). The  $f^{1/2}$  term is a low frequency correction that has little impact (i.e. less than 0.1dB) on the attenuation for frequencies greater than 0.772MHz and approaches an arbitrarily large value as f approaches zero. The pure skin effect model is modified to incorporate the high frequency correction and the baseline wander model is left to define the low frequency response. The transfer function for the modified cable model is given in equation 25.C-11.

$$H_{cable}(f) = e^{-(k_1 l \sqrt{f + k_2 l f})} e^{-jk_1 l \sqrt{f}}$$

The values of  $k_1$  and  $k_2$  can be derived from equation 25.C-10 assuming a linear increase in loss per unit length. These values are given in table 25.C-1.

| Parameter      | Value                   |  |

|----------------|-------------------------|--|

| k <sub>1</sub> | 2.265×10 <sup>-6</sup>  |  |

| k <sub>2</sub> | $2.648 \times 10^{-11}$ |  |

Table 25.C-1: Cable attenuation model parameters

Fast Ethernet Consortium

(Equation 25.C-11)

Note that  $k_1$  and  $k_2$  are also allowed to increase up to 0.4% per degree Celsius above room temperature (20°C) [8].

### <u>25.C.7 – Flat Loss</u>

Losses in transmission path that are not attributed to the skin effect are referred to as "flat". Flat losses can cause problems for equalizer strategies that assume a pure skin effect loss and use peak detection to determine the required equalization level. Four sources of flat loss are identified: transmit magnetics, PC card "dongles", connectors, and receive magnetics.

## **Transmit Magnetics**

The insertion loss of the transmit magnetics affects the amplitude of the signal launched into the channel. While this loss is not known, the amplitude of the signal at the 8-pin modular jack,  $V_{out}$ , is specified to be between 950 and 1050mV [2]. This can be translated to a flat loss (gain) relative to a nominal 1000mV transmit amplitude.

## PC Card "Dongles"