# **MODIFICATION RECORD**

July 2002 December 2004 February 2005 Initial Version First version for internal 10GEC review (0.3) First version for external review (0.4)

# ACKNOWLEDGMENTS

The University of New Hampshire would like to acknowledge the efforts of the following individuals and groups in the development of this test suite.

Eric LynskeyUniversity of New HampshireBob NoseworthyUniversity of New Hampshire

### INTRODUCTION

#### Overview

The University of New Hampshire InterOperability Laboratory (UNH-IOL) is an institution designed to improve the interoperability of standards based products by providing an environment where a product can be tested against other implementations of a standard. This suite of tests has been developed to help implementers evaluate the functioning of their Clause 49 Physical Coding Sublayer (PCS) based products. The tests do not determine if a product fully conforms to IEEE Std. 802.3ae-2002. Rather, they provide one method to isolate problems within a Clause 49 PCS device. Successful completion of all tests contained in this suite does not guarantee that the tested device will operate with other devices. However, combined with satisfactory operation in the UNH-IOL interoperability test bed, these tests provide a reasonable level of confidence that the Device Under Test (DUT) will function well in most environments.

#### **Organization of Tests**

The tests contained in this document are organized to simplify the identification of information related to a test and to facilitate in the actual testing process. Each test contains an identification section that describes the test and provides cross-reference information. The discussion section covers background information and specifies why the test is to be performed. Tests are grouped by similar functions and further organized by technology. Each test contains the following information:

### **Test Number**

The Test Number associated with each test follows a simple grouping structure. Listed first is the Test Group Number followed by the test's number within the group. This allows for the addition of future tests to the appropriate groups of the test suite without requiring the renumbering of the subsequent tests.

### Purpose

The purpose is a brief statement outlining what the test attempts to achieve. The test is written at the functional level.

#### References

The references section lists cross-references to IEEE 802.3 standards and other documentation that might be helpful in understanding and evaluating the test and results.

#### **Resource Requirements**

The requirements section specifies the hardware, and test equipment that will be needed to perform the test. The items contained in this section are special test devices or other facilities, which may not be available on all devices.

#### Last Modification

This specifies the date of the last modification to this test.

#### Discussion

The discussion covers the assumptions made in the design or implementation of the test as well as known limitations. Other items specific to the test are covered here.

# **Test Setup**

The setup section describes the configuration of the test environment. Small changes in the configuration should be included in the test procedure.

# Procedure

The procedure section of the test description contains the step-by-step instructions for carrying out the test. It provides a cookbook approach to testing, and may be interspersed with observable results.

### **Observable Results**

The observable results section lists specific items that can be examined by the tester to verify that the DUT is operating properly. When multiple values are possible for an observable result, this section provides a short discussion on how to interpret them. The determination of a pass or fail for a certain test is often based on the successful (or unsuccessful) detection of a certain observable result.

### **Possible Problems**

This section contains a description of known issues with the test procedure, which may affect test results in certain situations.

# TABLE OF CONTENTS

| MODIFICATION RECORD                                                                   |     |

|---------------------------------------------------------------------------------------|-----|

| ACKNOWLEDGMENTS                                                                       | II  |

| INTRODUCTION                                                                          | III |

| TABLE OF CONTENTS                                                                     |     |

| GROUP 1: SCRAMBLER/DESCRAMBLER AND BIT ORDERING                                       | 6   |

| Test 49.1.1: Transmit Scrambler                                                       | 7   |

| TEST 49.1.2: RECEIVE DESCRAMBLER                                                      | 8   |

| TEST 49.1.3: TRANSMIT BIT ORDERING                                                    | 9   |

| TEST 49.1.4: RECEIVE BIT ORDERING                                                     |     |

| GROUP 2: CODING RULES                                                                 |     |

| TEST 49.2.1: 64B/66B TRANSMITTER BLOCK ENCODER                                        |     |

| TEST 49.2.2: 64B/66B TRANSMITTER INVALID BLOCK HANDLING                               |     |

| TEST 49.2.3: 64B/66B RECEIVER BLOCK DECODING AND CONTROL CODE MAPPING                 |     |

| TEST 49.2.4: 64B/66B RECEIVER INVALID CODE HANDLING                                   |     |

| TEST 49.2.5: IDLE CONTROL CODE INSERTION/DELETION                                     |     |

| TEST 49.2.6: SEQUENCE ORDERED_SET DELETION                                            |     |

| GROUP 3: LOCK STATE MACHINE                                                           |     |

| TEST 49.3.1: IDENTIFICATION OF SYNC HEADER                                            |     |

| TEST 49.3.2: 64_GOOD                                                                  |     |

| TEST 49.3.3: 16_BAD                                                                   |     |

| GROUP 4: BER MONITOR STATE MACHINE                                                    |     |

| TEST 49.4.1: VALUE OF 125US_TIMER                                                     |     |

| <b>GROUP 5: TRANSMIT STATE MACHINE</b><br>TEST 49.5.1: IDENTIFICATION OF T TYPE(C)    |     |

| TEST 49.5.1: IDENTIFICATION OF 1_1 YPE(C)<br>TEST 49.5.2: IDENTIFICATION OF T TYPE(S) |     |

| TEST 49.5.2: IDENTIFICATION OF $T_TYPE(S)$                                            |     |

| TEST 49.5.3: IDENTIFICATION OF $T_TYPE(T)$                                            |     |

| TEST 49.5.4: IDENTIFICATION OF $T_TYPE(D)$                                            |     |

| TEST 49.5.6: TX INIT STATE                                                            |     |

| TEST 49.5.7: TX_INIT STATE                                                            |     |

| TEST 49.5.8: TX_D STATE                                                               |     |

| TEST 49.5.9: TX_D STATE<br>TEST 49.5.9: TX_T STATE                                    |     |

| TEST 49.5.10: TX E STATE                                                              |     |

| GROUP 6: RECEIVE STATE MACHINE                                                        |     |

| TEST 49.6.1: IDENTIFICATION OF R TYPE(C)                                              |     |

| TEST 49.6.2: IDENTIFICATION OF R TYPE(S)                                              |     |

| TEST 49.6.3: IDENTIFICATION OF R TYPE(T)                                              |     |

| TEST 49.6.4: IDENTIFICATION OF R TYPE(D)                                              |     |

| TEST 49.6.5: IDENTIFICATION OF R_TYPE(E)                                              |     |

| TEST 49.6.6: RX INIT STATE                                                            |     |

| Test 49.6.7: RX_C state                                                               |     |

| Test 49.6.8: RX_D state                                                               |     |

| TEST 49.6.9: RX_T STATE                                                               |     |

| TEST 49.6.10: RX_E STATE                                                              |     |

| GROUP 7: TEST PATTERN VERIFICATION                                                    | 54  |

| Test 49.7.1: Pseudo-random test pattern transmission                                  |     |

| TEST 49.7.2: PRBS31 TEST PATTERN TRANSMISSION                                         |     |

| TEST 49.7.3: SQUARE WAVE TEST PATTERN TRANSMISSION                                    |     |

| TEST 49.7.4: PSEUDO-RANDOM TEST PATTERN RECEPTION                                     |     |

| TEST 49.7.5: PRBS31 TEST PATTERN RECEPTION                                            |     |

| GROUP 8: MANAGEMENT                                                                   |     |

| GROUP 9: WIS, DELAY CONSTRAINTS AND OTHER                                             | 61  |

# **GROUP 1: Scrambler/Descrambler and Bit Ordering**

Scope: The following tests cover PCS operations specific to scrambling/descrambling and bit ordering.

**Overview:** These tests are designed to verify that the device under test properly scrambles/descrambles data, and properly orders data for serialization/deserialization.

# Test 49.1.1: Transmit Scrambler

**Purpose**: To verify the transmit scrambler polynomial.

# **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.6, Figure 49-8

## **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

Last Modification: February 15, 2005

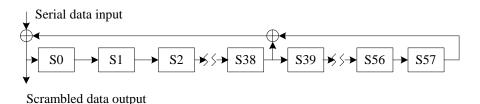

**Discussion**: Each encoded 66-bit block is passed through a 58-tap scrambler, with the sync bits removed, in order to randomly scramble the encoded data. The sync bits, which bypass the scrambler, are then added back to each scrambled 64-bit block to form the 66-bit block that will be transmitted onto the medium. The polynomial defining the scrambler is  $G(x) = 1+x^{39}+x^{58}$ . There is no requirement for an initial value to the scrambler, as the receiver will automatically be able to lock to the scrambler value. After passing through the scrambler, the 66-bit blocks are cut down to 16-bit blocks and these blocks are sent to the PMA to be serialized.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

# **Procedure:**

- 1. Instruct the DUT to transmit a stream of idle characters to the testing station.

- 2. The testing station should capture and analyze transmissions from the DUT.

# **Observable results:**

a. The DUT should use the defined scrambler polynomial.

# **Test 49.1.2: Receive Descrambler**

Purpose: To verify the receive descrambler polynomial.

# **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.10, Figure 49-10

## **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

Last Modification: February 15, 2005

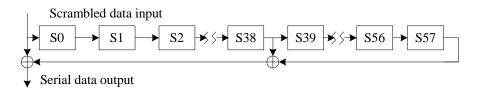

**Discussion**: On the receive side, the DUT must first deserialize the incoming bit stream into 16-bit blocks. These blocks are then analyzed such that the proper 66-bit boundary is found. Then, after stripping off the sync bits, the subsequent 64 bits are descrambled and then decoded. The descrambling polynomial used by the receiver is identical to the one used by the transmitter. Under normal conditions, the receiver will synchronize to the correct scrambler values after 64 bits have passed through the receiver. All bits following these initial 64-bits should be valid descrambled data.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

# **Procedure:**

- 1. Instruct the testing station to transmit properly ordered, encoded, and scrambled idle to the DUT.

- 2. Observe management indicators on the DUT, checking for a valid link indication.

- 3. Repeat steps 1-2, using idle that is invalidly scrambled, but otherwise correct.

#### **Observable results:**

- a. The DUT should be able to lock on to and recover properly scrambled data.

- b. The DUT should not be able to lock on to and recover improperly scrambled data.

# Test 49.1.3: Transmit bit ordering

**Purpose**: To verify the transmit bit ordering.

# **References**:

[1] IEEE Std 802.3ae-2002: Subclauses 49.2.7, Figures 49-2, and 49-5

## **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

# Last Modification: December 15, 2004

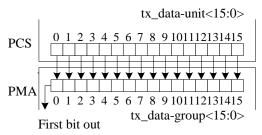

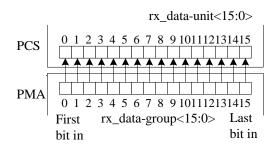

**Discussion**: The gearbox within the PCS is needed to convert between the 66-bit blocks of the PCS and the 16-bit blocks necessary for the PMA. The gearbox takes 66-bit blocks and converts them into 16-bit tx\_data-unit blocks, which are then passed to the PMA using the bit ordering shown below. Using For example, if the first sync bit of a 66-bit word maps to bit 0 of a tx\_data-unit, on the following 66-bit word the sync bits will map to bits 2 and 3 of the corresponding 16-bit word.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

# **Procedure:**

- 1. Instruct the DUT to transmit a stream of bits to the testing station.

- 2. The testing station should capture and analyze transmissions from the DUT.

#### **Observable results:**

a. The bit ordering of the DUT should match with Figures 49-2 and 49-5.

# Test 49.1.4: Receive bit ordering

**Purpose**: To verify the receive bit ordering.

## **References**:

[1] IEEE Std 802.3ae-2002: Subclauses 49.2.9, and 49.2.10, Figures 49-2, and 49-6

### **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

# Last Modification: December 15, 2004

**Discussion**: On the receive side, the DUT must first deserialize the incoming bit stream into 16-bit blocks. Each serial bit is concatenated to fill up rx\_data-group from bit 0 to bit 15 (the first bit received maps to bit 0). These blocks are then analyzed such that the proper 66-bit boundary is found.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

#### **Procedure:**

- 1. Instruct the testing station to transmit a valid bit stream to the DUT.

- 2. Observe management indicators on the DUT.

- 3. Repeat steps 1-2, instructing the testing station to transmit an otherwise valid bit stream but with bits in the wrong order (<15:0> instead of <0:15>).

#### **Observable results:**

- a. The DUT should be able to lock on to and recover with the correct bit ordering.

- b. The DUT should not be able to lock on to and recover data with an incorrect bit ordering.

# **GROUP 2: Coding Rules**

**Scope:** The following tests cover PCS operations specific to block coding/decoding.

**Overview:** These tests are designed to verify that the device under test properly encodes/decodes 64b/66b blocks as defined in Clause 49 of the IEEE 802.3.

## Test 49.2.1: 64B/66B Transmitter Block Encoder

Purpose: To verify that the DUT can properly transmit and encode valid 66-bit blocks.

### **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.4.6, Figure 49-7, Table 49-1

#### **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

# Last Modification: December 15, 2004

**Discussion:** When a device receives two consecutive transfers from the XGMII, it must encode the XGMII codes from 64-bits to 66-bits. Figure 49-7 lists all of the valid 66-bit block formats, including the sync headers, block type fields, data, and control codes. In total, there are 16 different valid data and control block combinations, as shown in Figure 49-7, for both data and control blocks. The DUT must be able to transmit all valid combinations of these blocks, and within each of the control blocks, the DUT should be able to transmit all valid combinations of the defined control codes in Table 49-1.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

### **Procedure:**

Part A: Valid 64B/66B Block Formats

- 1. Instruct the testing station to establish a valid link with the DUT.

- 2. Instruct the DUT to transmit valid bit streams to the testing station, containing one of the following blocks.

| $D_0D_1D_2D_3/D_4D_5D_6D$   | $O_0 D_1 D_2 D_3 / S_4 D_5 D_6 D_7$ | $T_0C_1C_2C_3/C_4C_5C_6C_7$ | $D_0D_1D_2D_3/T_4C_5C_6C_7$         |

|-----------------------------|-------------------------------------|-----------------------------|-------------------------------------|

| 7                           |                                     |                             |                                     |

| $C_0C_1C_2C_3/C_4C_5C_6C_7$ | $O_0 D_1 D_2 D_3 / O_4 D_5 D_6 D_6$ | $D_0T_1C_2C_3/C_4C_5C_6C_7$ | $D_0D_1D_2D_3/D_4T_5C_6C_7$         |

|                             | 7                                   |                             |                                     |

| $C_0C_1C_2C_3/O_4D_5D_6D_7$ | $S_0D_1D_2D_3/D_4D_5D_6D_7$         | $D_0D_1T_2C_3/C_4C_5C_6C_7$ | $D_0D_1D_2D_3/D_4D_5T_6C_7$         |

| $C_0C_1C_2C_3/S_4D_5D_6D_7$ | $O_0 D_1 D_2 D_3 / C_4 C_5 C_6 C_7$ | $D_0D_1D_2T_3/C_4C_5C_6C_7$ | $D_0 D_1 D_2 D_3 / D_4 D_5 D_6 T_7$ |

- 3. Observe all transmissions from the DUT.

- 4. Repeat steps 1-3, using each of the remaining valid blocks.

# Part B: Control Codes

- 1. Instruct the testing station to establish a valid link with the DUT.

- 2. Instruct the DUT to transmit one of the following blocks to the testing station:

| ſ | Syn | Block type | $C_0$ | C <sub>1</sub> | C <sub>2</sub> | C <sub>3</sub> | $C_4$ | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

|---|-----|------------|-------|----------------|----------------|----------------|-------|----------------|----------------|----------------|

|   | c   |            |       |                |                |                |       |                |                |                |

| Ī | 10  | 0x1E       | 0x00  | 0x2            | 0x33           | 0x4            | 0x55  | 0x66           | 0x78           | 0x00           |

|   |     |            |       | D              |                | В              |       |                |                |                |

| Ī | 10  | 0x1E       | 0x1   | 0x1E           | 0x1            | 0x1E           | 0x1   | 0x1            | 0x1            | 0x1            |

|   |     |            | Е     |                | E              |                | Е     | E              | Е              | E              |

- 3. Observe all transmissions from the DUT.

- 4. Repeat steps 1-3, sending the remaining block.

## Part C: O Codes

1. Instruct the testing station to establish a valid link with the DUT.

#### University of New Hampshire InterOperability Laboratory

2. Instruct the DUT to transmit one of the following blocks to the testing station:

| Syn | Block type | <b>D</b> <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | <b>O</b> <sub>1</sub> | O <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | <b>D</b> <sub>7</sub> |

|-----|------------|-----------------------|----------------|----------------|-----------------------|----------------|----------------|----------------|-----------------------|

| с   |            |                       |                |                |                       |                |                |                |                       |

| 10  | 0x55       | 0x00                  | 0x00           | 0x01           | 0x0                   | 0x0            | 0x00           | 0x00           | 0x01                  |

| 10  | 0x55       | 0x00                  | 0x00           | 0x01           | 0x0                   | 0xF            | 0x00           | 0x00           | 0x01                  |

| 10  | 0x55       | 0x00                  | 0x00           | 0x00           | 0xF                   | 0xF            | 0x00           | 0x00           | 0x0                   |

- 3. Observe all transmissions from the DUT.

- 4. Repeat steps 1-3, sending the remaining blocks.

### **Observable results:**

- a. The DUT should properly transmit and encode all valid 66-bit blocks.

- b. The DUT should properly transmit and encode all valid control codes.

- c. The DUT should properly transmit and encode all valid O codes.

**Possible Problems:** If an XGMII interface is not available, it may not be possible to perform all of the test cases in this test. In addition, it may take multiple attempts to see certain test vectors since there is no way to guarantee the alignment of the DUT (for example,  $O_0D_1D_2D_3/S_4D_5D_6D_7$  is equivalent to  $O_0D_1D_2D_3/O_4D_5D_6D_7$  followed by a  $S_0D_1D_2D_3/D_4D_5D_6D_7$ ).

## Test 49.2.2: 64B/66B Transmitter Invalid Block Handling

**Purpose:** To verify that the DUT does not transmit invalid blocks or control codes.

### **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.4.6, Figure 49-7, Table 49-1

#### **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

### Last Modification: February 15, 2005

**Discussion:** When a device receives two consecutive transfers from the XGMII, it must encode the XGMII codes from 64-bits to 66-bits. Figure 49-7 lists all of the valid 66-bit block formats, including the sync headers, block type fields, data, and control codes. All block types and control codes that are not listed in these locations are considered invalid, and should not be transmitted by the DUT.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

#### **Procedure:**

Case 1: Access to DUT through XGMII interface

- 1. Instruct the testing station to establish a valid link with the DUT.

- 2. Instruct the DUT to transmit bit streams to the testing station, containing one of the following blocks.

| $C_0C_1C_2C_3/D_4D_5D_6D_7$ | $C_0C_1C_2C_3/T_4C_5C_6C_7$ | $D_0 D_1 D_2 D_3 / S_4 D_5 D_6 D_7$ | $D_0D_1D_2D_3/O_4D_5D_6D$           |

|-----------------------------|-----------------------------|-------------------------------------|-------------------------------------|

|                             |                             |                                     | 7                                   |

| $T_0C_1C_2C_3/D_4D_5D_6D_7$ | $T_0C_1C_2C_3/S_4D_5D_6D_7$ | $T_0C_1C_2C_3/O_4D_5D_6D_7$         | $S_0D_1D_2D_3/C_4C_5C_6C_7$         |

| $S_0D_1D_2D_3/T_4C_5C_6C_7$ | $S_0D_1D_2D_3/O_4D_5D_6D$   | $O_0 D_1 D_2 D_3 / D_4 D_5 D_6 D_6$ | $O_0 D_1 D_2 D_3 / T_4 C_5 C_6 C_7$ |

|                             | 7                           | 7                                   |                                     |

| $T_0C_1C_2C_3/T_4C_5C_6C_7$ | $S_0D_1D_2D_3/S_4D_5D_6D_7$ |                                     |                                     |

- 3. Observe all transmissions from the DUT.

- 4. Repeat steps 1-3, using each of the remaining valid blocks.

#### Case 2: No access to DUT through XGMII interface

- 1. Instruct the testing station to establish a valid link with the DUT.

- 2. Instruct the DUT to transmit random sized frames with random contents.

- 3. Observe all transmissions from the DUT.

# **Observable results:**

Case 1

a. The DUT should encode all invalid blocks as errors.

Case 2

a. The DUT should never transmit invalid blocks.

**Possible Problems:** If an XGMII interface is not available, it may not be possible to perform all of the test cases in this test.

### Test 49.2.3: 64B/66B Receiver Block Decoding and Control Code Mapping

**Purpose:** To verify that the DUT can properly receive and decode valid 66-bit blocks.

### **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.4.6, Figure 49-7, Table 49-1

#### **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

### Last Modification: December 15, 2004

**Discussion**: When a device has descrambled a 66-bit block, it then must decode the block from 66 to 64 bits. Figure 49-7 lists all of the valid 66-bit block formats, including the sync headers, block type fields, data, and control codes. Received blocks that do not fit in that figure, and do not include the proper information from Table 49-1, are said to be invalid blocks. All other blocks are therefore valid, and should be properly received and decoded by the DUT. In total, there are 16 different valid data and control block combinations. There are 8 control code values explicitly called out in Table 49-1, out of a possible 128, given the 7-bit length of the field. The remaining 120 control codes are all invalid if received. However, all of the listed codes, even the reserved values, must be properly received by the PCS and decoded to the correct XGMII value.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

### **Procedure:**

Part A: Valid 66-bit blocks and control codes

- 1. Instruct the testing station to establish a valid link with the DUT.

- 2. Instruct the testing station to transmit a valid bit pattern to the DUT, containing one of the following blocks.

| $D_0D_1D_2D_3/D_4D_5D_6D$                                     | $O_0 D_1 D_2 D_3 / S_4 D_5 D_6 D_7$   | $T_0C_1C_2C_3/C_4C_5C_6C_7$ | $D_0D_1D_2D_3/T_4C_5C_6C_7$         |

|---------------------------------------------------------------|---------------------------------------|-----------------------------|-------------------------------------|

| $\frac{7}{C_0C_1C_2C_3/C_4C_5C_6C_7}$                         | $O_0 D_1 D_2 D_3 / O_4 D_5 D_6 D_6$   | $D_0T_1C_2C_3/C_4C_5C_6C_7$ | $D_0 D_1 D_2 D_3 / D_4 T_5 C_6 C_7$ |

| $C_0C_1C_2C_3/O_4D_5D_6D_7$                                   | $\frac{7}{S_0D_1D_2D_3/D_4D_5D_6D_7}$ | $D_0D_1T_2C_3/C_4C_5C_6C_7$ | $D_0D_1D_2D_3/D_4D_5T_6C_7$         |

| $\frac{C_0C_1C_2C_3/S_4D_5D_6D_7}{C_0C_1C_2C_3/S_4D_5D_6D_7}$ | $O_0 D_1 D_2 D_3 / C_4 C_5 C_6 C_7$   | $D_0D_1D_2T_3/C_4C_5C_6C_7$ | $D_0 D_1 D_2 D_3 / D_4 D_5 D_6 T_7$ |

- 3. Observe all management indications and responses from the DUT.

- 4. Repeat steps 1-3, using each of the remaining valid blocks.

#### Part B: Control Codes

- 5. Instruct the testing station to establish a valid link with the DUT.

- 6. Instruct the testing station to transmit one of the following blocks to the DUT:

| Syn | Block type | C <sub>0</sub> | C <sub>1</sub> | C <sub>2</sub> | C <sub>3</sub> | C <sub>4</sub> | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

|-----|------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| с   |            |                |                |                |                |                |                |                |                |

| 10  | 0x1E       | 0x00           | 0x2            | 0x33           | 0x4            | 0x55           | 0x66           | 0x78           | 0x00           |

|     |            |                | D              |                | В              |                |                |                |                |

| 10  | 0x1E       | 0x1            | 0x1E           | 0x1            | 0x1E           | 0x1            | 0x1            | 0x1            | 0x1            |

|     |            | E              |                | E              |                | E              | E              | E              | E              |

- 7. Observe all management indications and responses from the DUT.

- 8. Repeat steps 1-3, sending the remaining block.

# Part C: O Codes

- 5. Instruct the testing station to establish a valid link with the DUT.

- 6. Instruct the testing station to transmit one of the following blocks to the DUT:

| Syn | Block type | <b>D</b> <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | O <sub>1</sub> | $O_4$ | D <sub>5</sub> | D <sub>6</sub> | <b>D</b> <sub>7</sub> |

|-----|------------|-----------------------|----------------|----------------|----------------|-------|----------------|----------------|-----------------------|

| с   |            |                       |                |                |                |       |                |                |                       |

| 10  | 0x55       | 0x00                  | 0x00           | 0x01           | 0x0            | 0x0   | 0x00           | 0x00           | 0x01                  |

| 10  | 0x55       | 0x00                  | 0x00           | 0x01           | 0x0            | 0xF   | 0x00           | 0x00           | 0x01                  |

| 10  | 0x55       | 0x00                  | 0x00           | 0x00           | 0xF            | 0xF   | 0x00           | 0x00           | 0x0                   |

- 7. Observe all management indications and responses from the DUT.

- 8. Repeat steps 1-3, sending the remaining blocks.

# **Observable results:**

- a. The DUT should properly receive and decode all valid 66-bit blocks.

- b. The DUT should properly receive and decode all valid control codes.

- c. The DUT should properly receive and decode all valid O codes.

**Possible Problems:** If access to an interface above the PCS is not available, it may not be possible to verify that the received blocks properly decoded.

## Test 49.2.4: 64B/66B Receiver Invalid Code Handling

**Purpose:** To verify that the DUT properly handles the reception of invalid codes and blocks.

## **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.4.6, Figure 49-7, Table 49-1

### **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

### Last Modification: December 15, 2004

**Discussion**: When a device has descrambled a 66-bit block, it then must decode the block from 66 to 64 bits. Figure 49-7 lists all of the valid 66-bit block formats, including the sync headers, block type fields, data, and control codes. Received blocks that do not fit in that figure, and do not include the proper information from Table 49-1, are said to be invalid blocks. There are five conditions that indicate an invalid block exists: the sync header is invalid, the block type field contains a reserved value, an invalid control character is found, an invalid O code is found, there is no corresponding way to decode the block to the XGMII format.

Since there are only two valid possibilities for sync headers, '01' or '10', the other two combinations are invalid. Any 66-bit block that is received with a '00' or '11' sync header is therefore invalid. There are fifteen valid block type fields, each maintaining a 4-bit Hamming distance within the 8-bit field length. Each of the remaining 241 reserved block type fields are to be treated as invalid values. There are 8 control code values explicitly called out in Table 49-1, out of a possible 128, given the 7-bit length of the field. The remaining 120 control codes are all invalid if received. There are two valid O codes listed in the table, leaving 14 possible invalid O codes. Finally, there are 16 valid XGMII data and control block formats, and all others are to be received as invalid.

All invalid blocks should be completely replaced by the receiver with error control codes. These error codes are forwarded across the XGMII, and the RS will ensure that all frames received with errors are given a CRC error.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

# **Procedure:**

#### Part A – The sync field has a value of 00 or 11.

- 1. Instruct the testing station to establish a valid link with the DUT.

- 2. Instruct the testing station to transmit a frame to the DUT with one block of the frame using a sync header of '00' instead of '01'.

- 3. Observe all management indications and responses from the DUT.

- 4. Repeat steps 1-3, using a sync header of '11' in step 2.

#### Part B – The block type field contains a reserved value.

- 1. Instruct the testing station to establish a valid link with the DUT.

- 2. Instruct the testing station to transmit otherwise valid idle, but replacing the block type field of 0x1E with 0x00.

- 3. Observe all management indications and responses from the DUT.

- 4. Repeat steps 1-3, substituting the 0x00 with other reserved block type field values.

# Part C – Any control character contains a value not in Table 49-1

- 1. Instruct the testing station to establish a valid link with the DUT.

- 2. Instruct the testing station to transmit otherwise valid idle, but replacing the control code fields with 0x01.

- 3. Observe all management indications and responses from the DUT.

- 4. Repeat steps 1-3, substituting the 0x01 with other reserved control code values from Table 49-1.

# Part D – Any O code contains a value not in Table 49-1

- 1. Instruct the testing station to establish a valid link with the DUT.

- 2. Instruct the testing station to transmit continuous sequence ordered\_sets to the DUT, using a 10GBASE-R O code of 0x0, and indicating remote fault.

- 3. Observe all management indications and responses from the DUT.

- 4. Repeat steps 1-3, using a 10GBASE-R O Codes of 0x1 0xE.

### Part E – The set of eight XGMII characters does not have a corresponding block format in Figure 49-7.

- 1. Instruct the testing station to establish a valid link with the DUT.

- 2. Instruct the testing station to transmit a block containing one of the following encodings:

| $C_0C_1C_2C_3/D_4D_5D_6D_7$ | $C_0C_1C_2C_3/T_4C_5C_6C_7$ | $D_0D_1D_2D_3/S_4D_5D_6D_7$         | $D_0D_1D_2D_3/O_4D_5D_6D$           |

|-----------------------------|-----------------------------|-------------------------------------|-------------------------------------|

|                             |                             |                                     | 7                                   |

| $T_0C_1C_2C_3/D_4D_5D_6D_7$ | $T_0C_1C_2C_3/S_4D_5D_6D_7$ | $T_0C_1C_2C_3/O_4D_5D_6D_7$         | $S_0D_1D_2D_3/C_4C_5C_6C_7$         |

| $S_0D_1D_2D_3/T_4C_5C_6C_7$ | $S_0D_1D_2D_3/O_4D_5D_6D$   | $O_0 D_1 D_2 D_3 / D_4 D_5 D_6 D_6$ | $O_0 D_1 D_2 D_3 / T_4 C_5 C_6 C_7$ |

|                             | 7                           | 7                                   |                                     |

| $T_0C_1C_2C_3/T_4C_5C_6C_7$ | $S_0D_1D_2D_3/S_4D_5D_6D_7$ |                                     |                                     |

- 3. Observe all management indications and responses from the DUT.

- 4. Repeat steps 1-3, transmitting the other invalid blocks.

# **Observable results:**

- a. The DUT should replace the received blocks with EBLOCK\_R<71:0>, and should not receive the frame.

- b. The DUT should replace the received blocks with EBLOCK\_R<71:0>.

- c. The DUT should replace the received blocks with EBLOCK\_R<71:0>.

- d. The DUT should replace the received blocks with EBLOCK\_R<71:0>, and should not indicate reception of remote fault when receiving O codes that do not have a value of 0x0.

- e. The DUT should replace the received blocks with EBLOCK\_R<71:0>.

**Possible Problems:** If access to an interface above the PCS is not available, it may not be possible to verify that the received blocks are replaced with EBLOCK\_R. If the RS does not force frames received with error codes to have CRC errors, then additional indications may be needed.

### Test 49.2.5: Idle Control Code Insertion/Deletion

Purpose: To verify that the DUT properly inserts and delete idle

## **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.4.7

### **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

# Last Modification: February 15, 2005

**Discussion:** Idle control characters (/I/) are transmitted by the PCS when idle control characters are received from the XGMII. Idle characters may be added or deleted by the PCS to adapt between clock rates. /I/ insertion and deletion shall occur in groups of 4. /I/s may be added following idle or ordered sets. They shall not be added while data is being received. When deleting /I/s, the first four characters after a /T/ shall not be deleted.

As of February 15, 2005, this test is still under development.

### Test 49.2.6: Sequence Ordered\_set deletion

**Purpose:** To verify that the DUT properly deletes ordered\_sets.

## **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.4.10

### **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

# Last Modification: December 15, 2004

**Discussion:** Sequence ordered\_sets may be deleted by the PCS to adapt between clock rates. Such deletion shall only occur when two consecutive sequence ordered sets have been received, and only one of the two ordered sets may be deleted.

As of February 15, 2005, this test is still under development.

# **GROUP 3: Lock State Machine**

**Scope:** The following tests cover PCS operations specific to the Lock state machine (Figure 49-12)

**Overview:** These tests are designed to verify that the device under test properly compiles to and implements the Lock state diagram as defined in Clause 49 of the IEEE 802.3 standard.

## Test 49.3.1: Identification of sync header

Purpose: To verify that the DUT properly identifies valid and invalid sync headers.

## **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.13, Figure 49-12

### **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

### Last Modification: December 18, 2004

**Discussion:** Figure 49-12 defines the Lock state machine for the PCS. This state machine is used to determine the location of the sync headers, and therefore the 66-bit boundaries, within the incoming serial bit stream at the receiver of the DUT. The DUT tests various points of the bit stream and checks for two consecutive bits to be either a '01' or a '10', which signifies a valid sync header. When 64 consecutive valid sync headers are found, without any invalid sync headers, the DUT has high confidence that it has found the correct 66-bit boundary and then achieves block\_lock, and can begin to decode and receive data from its link partner. When block\_lock has been achieved, the DUT sets bit 3.33.15.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

### **Procedure:**

#### Part A: Valid sync headers

- 1. Bring the DUT to a state with the testing station such that no link is established.

- 2. Instruct the testing station to send a repeating pattern to the DUT containing a sync header of '10'.

- 3. Observe all management indications and responses from the DUT.

- 4. Repeat steps 1-3, using a sync header of '01'.

# Part B: Invalid sync headers

- 1. Bring the DUT to a state with the testing station such that no link is established.

- 2. Instruct the testing station to send a repeating pattern to the DUT containing a sync header of '00'.

- 3. Observe all management indications and responses from the DUT.

- 4. Repeat steps 1-3, using a sync header of '11'.

# **Observable results:**

- a. The DUT should achieve block\_lock while receiving an incoming bit stream with sync headers of '01' or '10'.

- b. The DUT should not achieve block\_lock while receiving an incoming bit stream with sync headers of '00' or '11'.

**Possible Problems:** If access to bit 3.33.15 is not available, this test cannot be performed.

# Test 49.3.2: 64\_GOOD

**Purpose:** To verify that the DUT needs to see 64 consecutive valid sync headers before achieving block\_lock.

# **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.13, Figure 49-12

# **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

# Last Modification: December 16, 2004

**Discussion:** Figure 49-12 defines the Lock state machine for the PCS. This state machine is used to determine the location of the sync headers, and therefore the 66-bit boundaries, within the incoming serial bit stream at the receiver of the DUT. The DUT tests various points of the bit stream and checks for two consecutive bits to be either a '01' or a '10', which signifies a valid sync header. When 64 consecutive valid sync headers are found, without any invalid sync headers, the DUT has high confidence that it has found the correct 66-bit boundary and then achieves block\_lock, and can begin to decode and receive data from its link partner. When block\_lock has been achieved, the DUT sets bit 3.33.15.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

### **Procedure:**

- 1. Bring the DUT to a state with the testing station such that no link is established.

- 2. Instruct the testing station to send a repeating idle pattern to the DUT containing 63 valid sync headers, followed by 1 invalid sync header.

- 3. Observe all management indications and responses from the DUT.

- 4. Repeat steps 1-3, increasing by one, the number of valid consecutive sync headers in step 2 until the DUT has been observed to achieve block\_lock, and set this value to *sh\_valid\_cnt*.

# **Observable results:**

a. The DUT should achieve block after receiving a continuous looping pattern of 64 or more valid sync headers, followed by a single invalid sync header.

**Possible Problems:** If access to bit 3.33.15 is not available, this test cannot be performed.

# Test 49.3.3: 16\_BAD

Purpose: To verify that the DUT needs to see 16 out of 64 invalid sync headers before slipping.

# **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.13, Figure 49-12

# **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

# Last Modification: December 16, 2004

**Discussion:** Figure 49-12 defines the Lock state machine for the PCS. This state machine is used to determine the location of the sync headers, and therefore the 66-bit boundaries, within the incoming serial bit stream at the receiver of the DUT. The DUT tests various points of the bit stream and checks for two consecutive bits to be either a '01' or a '10', which signifies a valid sync header. For any given set of 64 consecutive sync headers, if 16 are found to be invalid, the DUT has high confidence that it has not found the correct 66-bit boundary and must therefore slip, and check another location.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

# **Procedure:**

Part A: Determine number of consecutive invalid sync headers needed to slip

- 1. Bring the DUT to a state with the testing station such that no link is established.

- 2. Instruct the testing station to send a repeating idle pattern to the DUT containing *sh\_valid\_cnt* valid sync headers, so that the DUT may achieve block\_lock.

- 3. Instruct the testing station to transmit N consecutive blocks with valid sync headers, followed by M consecutive blocks with invalid sync headers to the DUT, following the completion of a full cycle of the repeating pattern in step 2 (the initial value of N is 0 and M is 15).

- 4. Observe all management indications and responses from the DUT.

- 5. Repeat steps 1-4, inserting a single incrementing the value of *N* from 0 to (*sh\_valid\_cnt-1*).

- 6. Repeat steps 1-5, resetting the initial value of N to 0, and incrementing the value of M by one until the DUT loses block\_lock, and set this value to *sh\_invalid\_cnt*.

# **Observable results:**

a. The DUT should lose block after receiving 16 invalid sync headers out of a group of 64 sync headers.

**Possible Problems:** If access to bit 3.33.15 is not available, this test cannot be performed.

# **GROUP 4: BER Monitor State Machine**

Scope: The following tests cover PCS operations specific to the BER Monitor state machine (Figure 49-12)

**Overview:** These tests are designed to verify that the device under test properly compiles to and implements the BER Monitor state diagram as defined in Clause 49 of the IEEE 802.3 standard.

## Test 49.4.1: Value of 125us\_timer

Purpose: To verify that the value of the 125us\_timer is between 93.75µs and 126.25µs.

### **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.13.2.5, Figure 49-13

### **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

# Last Modification: December 18, 2004

**Discussion:** The 125us\_timer described in Figure 49-13 must take on a value of  $125\mu s + 1\%$ , -25%. The timer is used to set the hi\_ber flag if more than 16 invalid sync headers are found within the window of  $125\mu s$ .

As of February 15, 2005 this test is still under development.

# **GROUP 5: Transmit State Machine**

**Scope:** The following tests cover PCS operations specific to the Transmit state machine (Figure 49-12)

**Overview:** These tests are designed to verify that the device under test properly compiles to and implements the Transmit state diagram as defined in Clause 49 of the IEEE 802.3 standard.

# Test 49.5.1: Identification of T\_TYPE(C)

**Purpose:** To verify that the DUT properly identifies the reception of T\_TYPE(C) vectors.

# **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.13, Figure 49-14

## **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

Last Modification: December 21, 2004

**Discussion:** One of the functions within the PCS is the T\_BLOCK\_TYPE function, which classifies each transmitted 72-bit tx\_raw vector as belonging to one of five possible types, depending on its contents. For a vector to be classified as C it must contain eight valid control characters other than /O/, /S/, /T/, and /E/; one valid ordered\_set and four valid control characters other than /O/, /S/, /T/, and /E/; one valid ordered\_set.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

# **Procedure:**

Part A: Eight control characters

- 1. Provide a bit stream across the XGMII such that the DUT is placed in the TX\_C state.

- 2. Provide the DUT with the following XGMII bit streams to transmit:

| $C_0$ | C <sub>1</sub> | $C_2$ | C <sub>3</sub> | $C_4$ | C <sub>5</sub> | C <sub>6</sub> | <b>C</b> <sub>7</sub> |

|-------|----------------|-------|----------------|-------|----------------|----------------|-----------------------|

| 0x07  | 0x07           | 0x07  | 0x07           | 0x07  | 0x07           | 0x07           | 0x07                  |

| 0x1C  | 0x3C           | 0x7   | 0xB            | 0xD   | 0xF7           | 0x07           | 0x07                  |

|       |                | С     | С              | С     |                |                |                       |

- 3. Monitor all management indications and transmissions of the DUT.

- 4. Repeat steps 1 3, transmitting the other test vector.

# Part B: Single ordered set and 4 control characters

- 1. Provide a bit stream across the XGMII such that the DUT is placed in the TX\_C state.

- 2. Provide the DUT with the following XGMII bit streams to transmit:

| $C_0$                 | $C_1$                 | $C_2$                 | C <sub>3</sub> | $O_4$          | <b>D</b> <sub>5</sub> | $D_6$          | <b>D</b> <sub>7</sub> |

|-----------------------|-----------------------|-----------------------|----------------|----------------|-----------------------|----------------|-----------------------|

| 0x07                  | 0x07                  | 0x07                  | 0x07           | 0x9C           | 0x00                  | 0x00           | 0x01                  |

| 0x07                  | 0x07                  | 0x07                  | 0x07           | 0x9C           | 0x00                  | 0x00           | 0x02                  |

| 0x07                  | 0x07                  | 0x07                  | 0x07           | 0x9C           | 0x12                  | 0x34           | 0x56                  |

| 0x1C                  | 0x3C                  | 0x7                   | 0xB            | 0x9C           | 0x00                  | 0x00           | 0x01                  |

|                       |                       | С                     | С              |                |                       |                |                       |

| 0x07                  | 0x07                  | 0x07                  | 0x07           | 0x5C           | 0x00                  | 0x00           | 0x01                  |

|                       |                       |                       |                |                |                       |                |                       |

| <b>O</b> <sub>0</sub> | <b>D</b> <sub>1</sub> | <b>D</b> <sub>2</sub> | D <sub>3</sub> | C <sub>4</sub> | C <sub>5</sub>        | C <sub>6</sub> | C <sub>7</sub>        |

| 0x9C                  | 0x00                  | 0x00                  | 0x01           | 0x07           | 0x07                  | 0x07           | 0x07                  |

| 0x9C                  | 0x00                  | 0x00                  | 0x02           | 0x07           | 0x07                  | 0x07           | 0x07                  |

| 0x9C                  | 0x12                  | 0x34                  | 0x56           | 0x07           | 0x07                  | 0x07           | 0x07                  |

| 0x9C                  | 0x00                  | 0x00                  | 0x01           | 0x1            | 0x3                   | 0x7            | 0xB                   |

|                       |                       |                       |                | С              | С                     | С              | С                     |

| 0x5C                  | 0x00                  | 0x00                  | 0x01           | 0x07           | 0x07                  | 0x07           | 0x07                  |

- 3. Monitor all management indications and transmissions of the DUT.

- 4. Repeat steps 1 3, transmitting the other test vectors.

### Part C: Two ordered sets

- 1. Instruct the DUT to provide valid idle to the DUT so that a link is established.

- 2. Provide the DUT with the following XGMII bit streams to transmit:

| $O_0$ | $D_1$ | D <sub>2</sub> | D <sub>3</sub> | $O_4$ | D <sub>5</sub> | D <sub>6</sub> | <b>D</b> <sub>7</sub> |

|-------|-------|----------------|----------------|-------|----------------|----------------|-----------------------|

| 0x9C  | 0x00  | 0x00           | 0x01           | 0x9C  | 0x00           | 0x00           | 0x01                  |

| 0x9C  | 0x00  | 0x00           | 0x02           | 0x9C  | 0x00           | 0x00           | 0x02                  |

| 0x9C  | 0x00  | 0x00           | 0x01           | 0x9C  | 0x00           | 0x00           | 0x02                  |

| 0x9C  | 0x00  | 0x00           | 0x02           | 0x9C  | 0x00           | 0x00           | 0x01                  |

| 0x9C  | 0x00  | 0x00           | 0x01           | 0x9C  | 0x12           | 0x34           | 0x56                  |

| 0x9C  | 0x12  | 0x34           | 0x56           | 0x9C  | 0x00           | 0x00           | 0x01                  |

| 0x9C  | 0x00  | 0x00           | 0x02           | 0x9C  | 0x12           | 0x34           | 0x56                  |

| 0x9C  | 0x12  | 0x34           | 0x56           | 0x9C  | 0x00           | 0x00           | 0x02                  |

| 0x5C  | 0x00  | 0x00           | 0x00           | 0x9C  | 0x00           | 0x00           | 0x01                  |

| 0x9C  | 0x00  | 0x00           | 0x01           | 0x5C  | 0x00           | 0x00           | 0x00                  |

| 0x5C  | 0x00  | 0x00           | 0x00           | 0x9C  | 0x00           | 0x00           | 0x02                  |

| 0x9C  | 0x00  | 0x00           | 0x02           | 0x5C  | 0x00           | 0x00           | 0x00                  |

| 0x9C  | 0x12  | 0x34           | 0x56           | 0x5C  | 0x00           | 0x00           | 0x00                  |

| 0x5C  | 0x00  | 0x00           | 0x00           | 0x9C  | 0x12           | 0x34           | 0x56                  |

| 0x5C  | 0x00  | 0x00           | 0x00           | 0x5C  | 0x00           | 0x00           | 0x00                  |

- 3. Monitor all management indications and transmissions of the DUT.

- 4. Repeat steps 1 3, transmitting the other test vectors.

#### **Observable results:**

- a. The DUT should properly encode all 72-bit vectors.

- b. The DUT should properly encode all 72-bit vectors.

- c. The DUT should properly encode all 72-bit vectors.

# Test 49.5.2: Identification of T\_TYPE(S)

**Purpose:** To verify that the DUT properly identifies the reception of T\_TYPE(S) vectors.

## **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.13, Figure 49-14

### **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

Last Modification: December 21, 2004

**Discussion:** One of the functions within the PCS is the T\_BLOCK\_TYPE function, which classifies each transmitted 72-bit tx\_raw vector as belonging to one of five possible types, depending on its contents. For a vector to be classified as S it must contain an /S/ in the first or fifth character, and any characters before the S character are valid control characters other than /O/, /S/, and /T/, or form a valid ordered\_set, and all characters following the /S/ are data characters.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

# Procedure:

Part A: S in first character

- 1. Provide a bit stream across the XGMII such that the DUT is placed in the TX\_C state.

- 2. Provide the DUT with the following XGMII bit streams to transmit:

| $S_0$ | <b>D</b> <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | $D_4$ | D <sub>5</sub> | $D_6$ | D <sub>7</sub> |

|-------|-----------------------|----------------|----------------|-------|----------------|-------|----------------|

| 0xF   | 0x55                  | 0x55           | 0x55           | 0x55  | 0x55           | 0x55  | 0xD            |

| В     |                       |                |                |       |                |       | 5              |

- 3. Monitor all management indications and transmissions of the DUT.

- 4. Repeat steps 1 3, transmitting the other test vector.

#### Part B: S in fifth character

- 1. Provide a bit stream across the XGMII such that the DUT is placed in the TX\_C state.

- 2. Provide the DUT with the following XGMII bit streams to transmit:

| $C_0$ | C <sub>1</sub> | C <sub>2</sub> | C <sub>3</sub> | $S_4$ | D <sub>5</sub> | D <sub>6</sub> | <b>D</b> <sub>7</sub> |

|-------|----------------|----------------|----------------|-------|----------------|----------------|-----------------------|

| 0x07  | 0x07           | 0x07           | 0x07           | 0xF   | 0x55           | 0x55           | 0x55                  |

|       |                |                |                | В     |                |                |                       |

| 0x1C  | 0x3C           | 0x7            | 0xB            | 0xF   | 0x55           | 0x55           | 0x55                  |

|       |                | С              | С              | В     |                |                |                       |

| <b>O</b> <sub>0</sub> | <b>D</b> <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | $S_4$    | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> |

|-----------------------|-----------------------|----------------|----------------|----------|----------------|----------------|----------------|

| 0x9C                  | 0x00                  | 0x00           | 0x01           | 0xF<br>B | 0x55           | 0x55           | 0x55           |

| 0x9C                  | 0x00                  | 0x00           | 0x02           | 0xF<br>B | 0x55           | 0x55           | 0x55           |

| 0x9C                  | 0x12                  | 0x34           | 0x56           | 0xF<br>B | 0x55           | 0x55           | 0x55           |

| 0x5C                  | 0x00                  | 0x00           | 0x00           | 0xF<br>B | 0x55           | 0x55           | 0x55           |

- 3. Monitor all management indications and transmissions of the DUT.

- 4. Repeat steps 1 3, transmitting the other test vectors.

### **Observable results:**

- a. The DUT should properly encode all 72-bit vectors.

- b. The DUT should properly encode all 72-bit vectors.

# Test 49.5.3: Identification of T\_TYPE(T)

**Purpose:** To verify that the DUT properly identifies the reception of T\_TYPE(T) vectors.

# **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.13, Figure 49-14

# **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

# Last Modification: December 21, 2004

**Discussion:** One of the functions within the PCS is the T\_BLOCK\_TYPE function, which classifies each transmitted 72-bit tx\_raw vector as belonging to one of five possible types, depending on its contents. For a vector to be classified as T it must contain a /T/ in one of the eight characters. All characters before the /T/ must be data characters, and all characters following the /T/ are valid control characters other than /O/, /S/, and /T/.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

# **Procedure:**

- 1. Provide a bit stream across the XGMII such that the DUT is placed in the RX\_D state.

- 2. Instruct the DUT to transmit the first of the following 72-bit vectors to the testing station, and using 0x07 for all control characters:

| $T_0C_1C_2C_3/C_4C_5C_6C_7$ | $D_0D_1D_2D_3/T_4C_5C_6C_7$         |

|-----------------------------|-------------------------------------|

| $D_0T_1C_2C_3/C_4C_5C_6C_7$ | $D_0D_1D_2D_3/D_4T_5C_6C_7$         |

| $D_0D_1T_2C_3/C_4C_5C_6C_7$ | $D_0D_1D_2D_3/D_4D_5T_6C_7$         |

| $D_0D_1D_2T_3/C_4C_5C_6C_7$ | $D_0 D_1 D_2 D_3 / D_4 D_5 D_6 T_7$ |

- 3. Monitor all management indications and transmissions of the DUT.

- 4. Repeat steps 1 3, transmitting the other test vectors.

- 5. Repeat steps 1 4, replacing the 0x07 with other valid control characters.

# **Observable results:**

a. The DUT should properly encode all 72-bit vectors.

# Test 49.5.4: Identification of T\_TYPE(D)

**Purpose:** To verify that the DUT properly identifies the reception of T\_TYPE(D) vectors.

# **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.13, Figure 49-14

# **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

# Last Modification: December 21, 2004

**Discussion:** One of the functions within the PCS is the T\_BLOCK\_TYPE function, which classifies each transmitted 72-bit tx\_raw vector as belonging to one of five possible types, depending on its contents. For a vector to be classified as D it must contain eight data characters.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

# **Procedure:**

Part A: Transmit all valid data codes

- 1. Provide a bit stream across the XGMII such that the DUT is placed in the RX\_D state.

- 2. Instruct the DUT to transmit all valid data blocks to the testing station, encompassed within valid frames.

- 3. Monitor all management indications and transmissions of the DUT.

# **Observable results:**

a. The DUT should properly encode all 72-bit vectors.

# Test 49.5.5: Identification of T\_TYPE(E)

**Purpose:** To verify that the DUT properly identifies the reception of T\_TYPE(E) vectors.

# **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.13, Figure 49-14

# **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

Last Modification: December 21, 2004

**Discussion:** One of the functions within the PCS is the T\_BLOCK\_TYPE function, which classifies each transmitted 72-bit tx\_raw vector as belonging to one of five possible types, depending on its contents. For a vector to be classified as E it must not meet the criteria for any other value (C, S, T, or D). In any block that contains errors, the entire block is replaced with 8 XGMII error control characters.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

# **Procedure:**

Part A: C Block containing E

- 1. Provide a bit stream across the XGMII such that the DUT is placed in the RX\_C state.

- 2. Provide the DUT with the following XGMII bit streams to transmit:

| C <sub>0</sub> | C <sub>1</sub> | $C_2$ | C <sub>3</sub> | $C_4$ | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

|----------------|----------------|-------|----------------|-------|----------------|----------------|----------------|

| 0x07           | 0x07           | 0x07  | 0x07           | 0x07  | 0x07           | 0x07           | 0xFE           |

| 0x07           | 0x07           | 0x07  | 0x07           | 0x07  | 0x07           | 0xF            | 0x07           |

|                |                |       |                |       |                | E              |                |

| 0x07           | 0x07           | 0x07  | 0x07           | 0x07  | 0xF            | 0x07           | 0x07           |

|                |                |       |                |       | E              |                |                |

| 0x07           | 0x07           | 0x07  | 0x07           | 0xF   | 0x07           | 0x07           | 0x07           |

|                |                |       |                | E     |                |                |                |

| 0x07           | 0x07           | 0x07  | 0xF            | 0x07  | 0x07           | 0x07           | 0x07           |

|                |                |       | E              |       |                |                |                |

| 0x07           | 0x07           | 0xF   | 0x07           | 0x07  | 0x07           | 0x07           | 0x07           |

|                |                | E     |                |       |                |                |                |

| 0x07           | 0xFE           | 0x07  | 0x07           | 0x07  | 0x07           | 0x07           | 0x07           |

| 0xFE           | 0x07           | 0x07  | 0x07           | 0x07  | 0x07           | 0x07           | 0x07           |

- 3. Monitor all management indications and transmissions of the DUT.

- 4. Repeat steps 1 3, transmitting the other test vectors.

# **Observable results:**

a. The DUT should properly encode all 72-bit vectors as T\_BLOCK\_TYPE(E).

# Test 49.5.6: TX\_INIT state

**Purpose:** To verify that the DUT properly behaves while in the TX\_INIT state.

# **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.13, Figure 49-14

# **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

# Last Modification: February 15, 2005

**Discussion:** When the DUT has been reset, it returns to the TX\_INIT state, and begins the continuous transmission of local fault blocks. It will remain in this state until the reset condition has passed. Under normal conditions, the DUT will not transmit local fault across the link, but a small number of these blocks will be transmitted when the DUT is in the TX\_INIT state.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

# **Procedure:**

Part A: Transmission of local fault

- 1. Through MDIO access or other means, force the DUT to reset itself.

- 2. Monitor all management indications and transmissions of the DUT.

# Part B: Transmission of words following reset

- 1. Through MDIO access or other means, force the DUT to reset itself.

- 2. While in the TX\_INIT state, force the DUT to transmit an S.

- 3. Monitor all management indications and transmissions of the DUT.

- 4. Repeat steps 1 3, forcing the DUT to transmit the following codes: C, E, D, T.

# **Observable results:**

- a. When being reset, the DUT should continuously transmit local fault blocks.

- b. The DUT should transmit the appropriate words when exiting the TX\_INIT state.

**Possible Problems:** If no mechanism is available to transmit data across the XGMII interface, it may not be possible to perform this test. Other methods, including the use of loopbacks may be used to complete parts of the test. If access to MDIO or other means to reset the device are not available, this test cannot be performed.

# Test 49.5.7: TX\_C state

**Purpose:** To verify that the DUT properly behaves while in the TX\_C state.

# **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.13, Figure 49-14

# **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

# Last Modification: December 21, 2004

**Discussion:** When the transmitter of the DUT has completed the transmission of local fault blocks, and when valid C blocks are being observed at the XGMII interface, the DUT will enter the TX\_C state in Figure 49-14. The DUT will remain in this state as long as valid idle or sequence ordered\_sets are being transmitted across the XGMII. Upon the transmission of an S block, the DUT will transition to the TX\_D state. Transmission of E, D, or T blocks will force the DUT to the TX\_E state.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

# **Procedure:**

# Part A: Transmission of C

- 1. Provide a bit stream across the XGMII such that the DUT is placed in the TX\_C state.

- 2. Instruct the DUT to transmit a valid C block to the testing station.

- 3. Monitor all management indications and transmissions of the DUT.

# Part B: Transmission of S

- 1. Provide a bit stream across the XGMII such that the DUT is placed in the RX\_C state.

- 2. Instruct the DUT to transmit a valid S block to the testing station.

- 3. Monitor all management indications and transmissions of the DUT.

# Part C: Transmission of E, D, or T

- 1. Provide a bit stream across the XGMII such that the DUT is placed in the RX\_C state.

- 2. Instruct the DUT to transmit a valid E block to the testing station.

- 3. Monitor all management indications and transmissions of the DUT.

- 4. Repeat steps 1 3, transmitting valid D and T blocks to the DUT.

# **Observable results:**

- a. The DUT should properly encode all 72-bit vectors and remain in the TX\_C state while transmitting C blocks.

- b. The DUT should properly encode all 72-bit vectors and transition to the TX\_D state while transmitting an S block.

- c. The DUT should properly encode all 72-bit vectors and transition to the TX\_E state when transmitting E, D, or T blocks.

# Test 49.5.8: TX\_D state

**Purpose:** To verify that the DUT properly behaves while in the TX\_D state.

# **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.13, Figure 49-14

# **Resource Requirements:**

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

# Last Modification: December 21, 2004

**Discussion:** When valid C blocks are being observed, within the TX\_C state, the DUT will enter the TX\_D state in Figure 49-14 upon the transmission of an S block. The DUT will remain in the TX\_D state as long as valid D blocks are being received. The DUT will transition to the TX\_T state upon transmission of a T block. The DUT will transition to the TX\_E state upon transmission of an E, C, or S block.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

# **Procedure:**

Part A: Transmission of D

- 1. Provide a bit stream across the XGMII such that the DUT is placed in the TX\_D state.

- 2. Instruct the testing station to transmit a valid D block to the DUT.

- 3. Monitor all management indications and transmissions of the DUT.

### Part B: Transmission of T

- 1. Provide a bit stream across the XGMII such that the DUT is placed in the TX\_D state.

- 2. Instruct the DUT to transmit a valid T block to the testing station.

- 3. Monitor all management indications and transmissions of the DUT.

# Part C: Reception of E or C or S

- 1. Provide a bit stream across the XGMII such that the DUT is placed in the TX\_D state.

- 2. Instruct the DUT to transmit a valid E block to the test station.

- 3. Monitor all management indications and transmissions of the DUT.

- 4. Repeat steps 1 3, transmitting a valid C block in step 2, then again with an S block.

# **Observable results:**

- a. The DUT should properly encode all 72-bit vectors and remain in the TX\_D state.

- b. The DUT should properly encode all 72-bit vectors and transition to the TX\_T state.

- c. The DUT should properly encode all 72-bit vectors and transition to the TX\_E state.

# Test 49.5.9: TX\_T state

**Purpose:** To verify that the DUT properly behaves while in the TX\_T state.

# **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.13, Figure 49-14

# **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

# Last Modification: December 21, 2004

**Discussion:** When valid D blocks are being observed at the 66-bit level, the DUT will enter the TX\_T state in Figure 49-14 upon the reception of a T block. Once the TX\_T state is entered, the DUT will transition to either the TX\_C, TX\_D, or TX\_E state, depending on the next code.

**Test Setup**: Connect the device under test (DUT) to the testing station (transmit to receive, receive to transmit) with the appropriate medium (i.e. single mode fiber, etc.).

# **Procedure:**

Part A: Transmission of C

- 1. Provide a bit stream across the XGMII such that the DUT is placed in the RX\_T state.

- 2. Instruct the DUT to transmit a valid C block to the testing station.

- 3. Monitor all management indications and transmissions of the DUT.

# Part B: Transmission of S

- 1. Provide a bit stream across the XGMII such that the DUT is placed in the RX\_C state.

- 2. Instruct the DUT to transmit a valid S block to the testing station.

- 3. Monitor all management indications and transmissions of the DUT.

# Part C: Transmission of E, D, or T

- 1. Provide a bit stream across the XGMII such that the DUT is placed in the RX\_C state.

- 2. Instruct the DUT to transmit a valid E block to the testing station.

- 3. Monitor all management indications and transmissions of the DUT.

- 4. Repeat steps 1 3, transmitting a valid D block in step 2, then again with a T block.

# **Observable results:**

- a. The DUT should properly encode all 72-bit vectors, and transition to the TX\_C state.

- b. The DUT should properly encode all 72-bit vectors, and transition to the TX\_D state.

- c. The DUT should properly encode all 72-bit vectors, and transition to the TX\_E state.

### Test 49.5.10: TX\_E state

**Purpose:** To verify that the DUT properly behaves while in the TX\_E state.

# **References**:

[1] IEEE Std 802.3ae-2002: Subclause 49.2.13, Figure 49-14

# **Resource Requirements**:

• A testing station capable of encoding (decoding) 64 bit octets to (from) 66-bit code groups as specified in Clause 49 and sending (receiving) these code groups using the signaling method described in Clause 52.

# Last Modification: December 21, 2004