#### Clause 40

#### 1000BASE-T Physical Medium Attachment (PMA) Sublayer

© UNIVERSITY of NEW HAMPSHIRE INTEROPERABILITY LABORATORY

#### **Presentation Overview:**

- Location in the OSI stack

- Interface with PCS

- Interface with Auto-Negotiation

- PAM-5 Encoding Scheme

- PMA Sublayers Functionality and Functions

- PMA Electrical Specifications

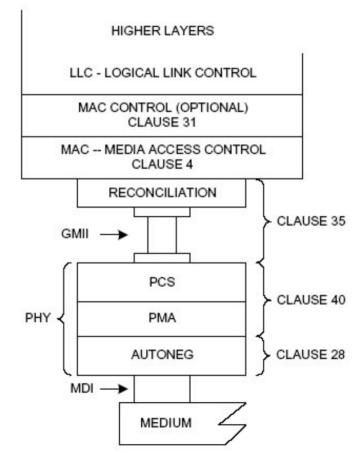

#### PMA in the OSI Model

LAN CSMA/CD LAYERS

# OSI: PCS

- Transmits 8-bit code groups in parallel at 125 MHz for the PMA to serialize

- Translates the data to be sent into a suitable form.

- The PCS operating functions are:

- PCS Transmit Enable, PCS Transmit, PCS Receive, and PCS Carrier Sense

- PCS passes the 4D 5 level (+2, +1, 0, -1, -2) coding to the PMA to convert to electrical signaling

# OSI: PMA (General Role)

•The PMA is the interface between the PCS and Autonegotiation

•Primary role is to Serialize and De-serialize the incoming data stream coming to and from the MDI

•Implements PAM-5 (Voltage dependant signaling between MDI/PMA)

Controls Partial Response

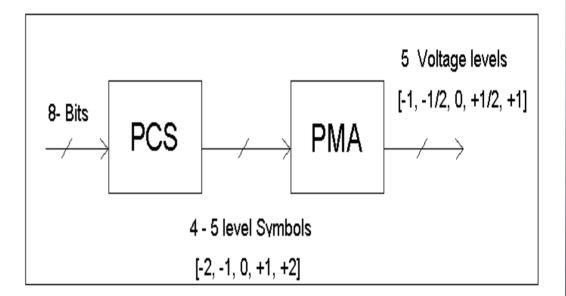

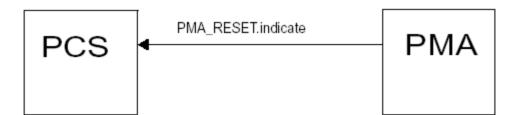

# OSI: PCS/PMA

- Shown here is the basic interface between the PCS and PMA

- The PCS takes in 8 bits of parallel data and sends the PMA 4, "5 level symbols" which can take on the values shown

- The PMA adds partial response and converts the quinary symbols to PAM-5 signaling to interface with the MDI, taking on the values shown

UNIVERSITY of NEW HAMPSHIRE INTEROPERABILITY LABORATORY

# **OSI:** Auto-Negotiation

- Required for 1000Base-T Operation

- Advertise Abilities

- Transmission speeds

- Half and/or Full Duplex

- Determine Master and Slave relationship

- Uses prioritization scheme

- Base page, Next page, etc... To establish fast possible link (1000Mb/s)

- Needed for PHY Control, a PMA subfunction

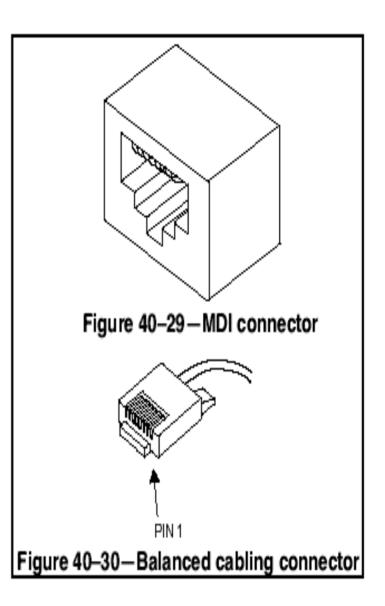

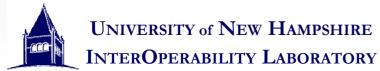

# OSI: MDI/MDI-X

Medium Dependant Interface

•MDI is specified as the mechanical interface to the balanced cabling for 1000Base-T Ethernet

|                                 | PMA signal to MDI and MDI-X pin-outs |

|---------------------------------|--------------------------------------|

| I Janie 4(12722 Assignment of P |                                      |

|                                 |                                      |

| Contact | MDI    | MDI-X  |

|---------|--------|--------|

| 1       | BI_DA+ | BI_DB+ |

| 2       | BI_DA- | BI_DB- |

| 3       | BI_DB+ | BI_DA+ |

| 4       | BI_DC+ | BI_DD+ |

| 5       | BI_DC- | BI_DD- |

| 6       | BI_DB- | BI_DA- |

| 7       | BI_DD+ | BI_DC+ |

| 8       | BI_DD- | BI_DC- |

# OSI: Automatic MDI/MDI-X

- Purpose (optional)

- The main role of the Automatic MDI/MDI-X is to eliminate the need for using crossover cables

- Able to randomly switch between MDI and MDI-X configuration after listening for Fast Link Pulses (FLPs) for a specified amount of time (62 ±2 ms)

- The MDI and PMA use a modulation scheme over each pair which is called, 5-level Pulse Amplitude Modulation (PAM-5)

- PAM5 signaling

- Five discrete voltage levels  $[-1, -\frac{1}{2}, 0, +\frac{1}{2}, +1]$  volts

- Lowers signaling bandwidth

- Allows for 2 bits per symbol

- The PAM-5 Implementation is intrinsic in achieving 1000Mb/s

- 125 MHz signaling rate

(As proven over CAT-5 by 100Base-TX)

- Using PAM-5 @ 2 bits per symbol

- Use all 4 pairs of CAT 5 cable

- Results in:

= x 2 <u>= x 4</u> 1000 Mb/s

= 125

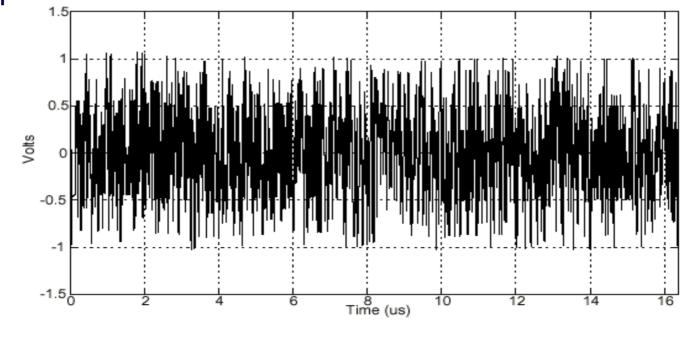

- Partial Response acts like a digital filter

- This is accomplished by introducing a known ISI (Inter symbol Interference)

- Digital filter is applied to transmitted PAM5 symbol stream

$F(Z) = \frac{3}{4}(Z_n) + \frac{1}{4}(Z_{n-1})$

- Where  $\boldsymbol{z}_n$  is the current symbol, and  $\boldsymbol{z}_{n\text{-}1}$  is the previous

- This Equation yields up to 17 different discrete voltage levels

- In 1/8 V increments

•An example of the 17 possible discrete voltage levels created by the Partial Response filter

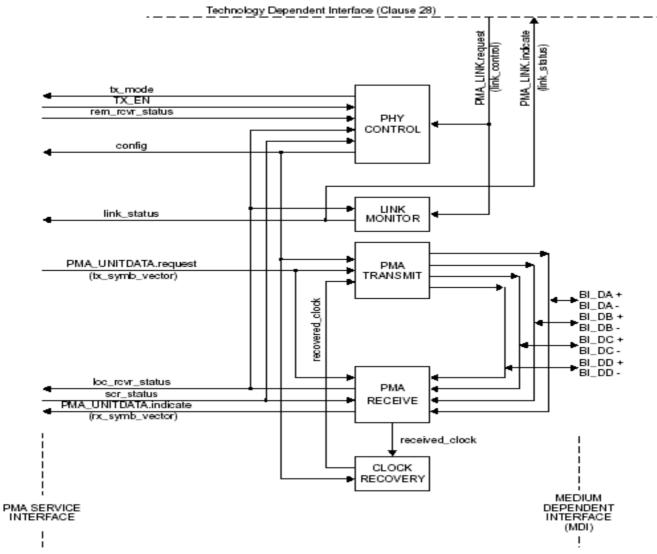

# PMA Sub functions

- There are six PMA sublayer functions, starting with PMA reset, followed by 5 other simultaneous operating functions that make this possible

- Six functions:

- PMA Reset

- PMA Transmit

- PMA Receive

- PMA PHY Control

- Link Monitor

- Clock Recovery

(40.4.2.1)(40.4.2.2)(40.4.2.3)(40.4.2.4)(40.4.2.5)(40.4.2.6)

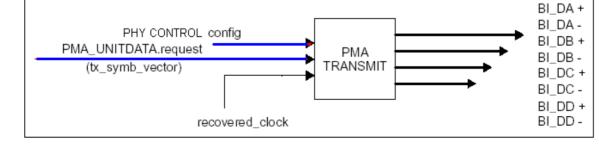

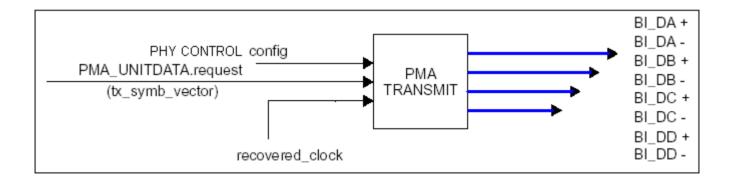

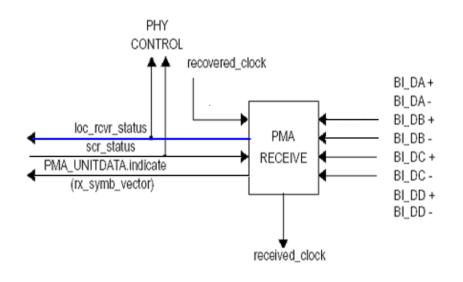

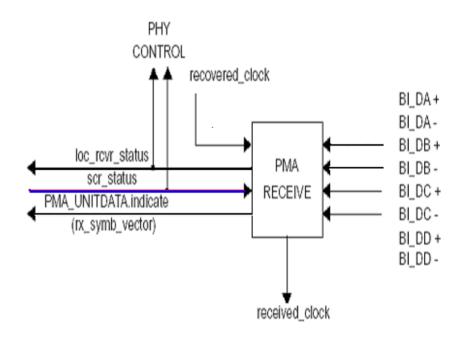

NOTE The recovered\_clock arc is shown to indicate delivery of the recovered clock signal back to PMA TRANSMIT for loop timing.

Figure 40–13 – PMA reference diagram

# PMA Function: PMA Reset

- Initialization

- What does it do?

- What makes it happen?

## PMA Function: PMA Reset

- Initializes the start of the other 5 simultaneous operating functions

- Used for control to restart the 5 functions including the clock recovery

## PMA Function: PMA Reset

- PMA Reset is executed when one of these occurs

- Power on

- A request from the management entity

- PMA Reset sets PCS\_RESET=ON while one or both of the above conditions are true

- PCS\_RESET.Indicate can take one of two states, TRUE or FALSE. Where Reset is enabled when TRUE, and visa-versa

- The Transmit function characteristics are composed of:

- Transmitters

- Continuous MDI Transmitting

- Transmit clock

- Jitter Conformance

- During Transmission,

- PMA\_UNITDATA.request conveys to the PMA using tx\_symb\_vector the value of the symbols to be sent over each of the 4 transmit pairs

- The tx\_symb\_vector parameter takes the following from:

- SYMB\_4D (a vector of 4 quinary symbols, one for each pair)

- Upon receipt of this primitive the PMA transmits on to the MDI the signals corresponding to the quinary signals received

- PHY CONTROL Config can consist of:

- Tx\_mode= SEND\_N (Normal GMII Data stream, Control information, or idle)

SEND\_I (Transmit of Idle code group)

SEND\_Z (Transmit of Zero code group)

- Uses four synchronous transmitters to generate the PAM5 signals on each of the four pairs, BI\_DA, BI\_DB, BI\_DC, and BI\_DD

- The Signals generated by the PMA Transmit also fit the PAM5 specifications for conformance with the MDI

- The four transmitters shall be driven by the same transmit clock:

- TX\_TCLK

- The TX\_TCLK, known as the transmit clock is the reference clock for the MASTER. This is later discussed as a source for Jitter testing

- Conforms to Jitter specifications with respect to the two conditions, Master/Slave

- When PMA\_CONFIG indicates MASTER mode, the PMA Transmit Function will source the TX\_TCLK from a Local Clock Source

- When PMA\_CONFIG indicates SLAVE mode, the PMA Transmit Function will source the TX\_TCLK from the <u>Recovered Clock</u> while meeting the Jitter requirements

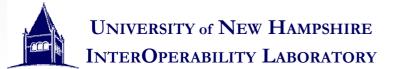

- Three primary PMA Receive Characteristics are shown Below:

- Receivers

- Abilities

- Sub-Functions

- Comprises four independent receivers for quinary PAM signals on each of the four pairs

BI\_DA, BI\_DB, BI\_DC, and BI\_DD

- Has the ability to translate the signals received on all pairs into the PMA\_UNIDATA.indicate parameter rx\_symb\_vector with a bit error rate less than or equal to 10<sup>-10</sup>

- Contains necessary circuitry to:

- Detect quinary symbol sequences from the signals received at the MDI over all four receive pairs

- Present the sequences to the PCS Receive function

- PMA Receive has the following sub-functions:

- Signal Equalization, Echo and Crosstalk Cancellation, and Sequence estimation

- These Sub-Functions are used to determine the receiver performance and generate loc\_rcvr\_status (general status of local receiver) variables.

Loc\_rcvr\_status: This primitive is generated by PMA Receive to indicate the status of the receive link at the local PHY The parameter loc\_rcvr\_status conveys to the PCS Transmit, PCS Receive, PMA PHY Control function, and Link Monitor the information on whether the status of the overall received link is satisfactory or not.

#### SCR\_STATUS

- This primitive is generated by PCS Receive to communicate the status of the descrambler for the local PHY

- The parameter scr\_status conveys to the PMA Receive function that the descrambler has achieved synchronization.

- Tasks of PMA PHY Control:

- Generates the control actions needed to bring the PHY into the mode of operation when frames can be exchanged with the link partner.

- Disables the Transmitter state during Auto-Negotiation

- Forces Master and Slave control after Auto-Negotiation and starts the respective timers

- Generates signals that control the PCS and PMA sublayer operations

- It determines whether the PHY operates in a normal state, enabling data transmission over the link segment, or whether the PHY sends special code-groups that represent the idle mode

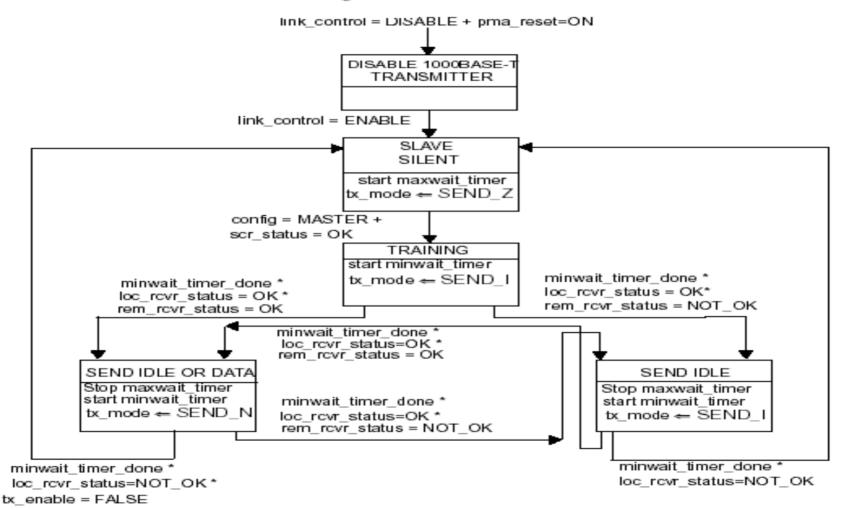

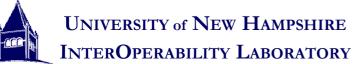

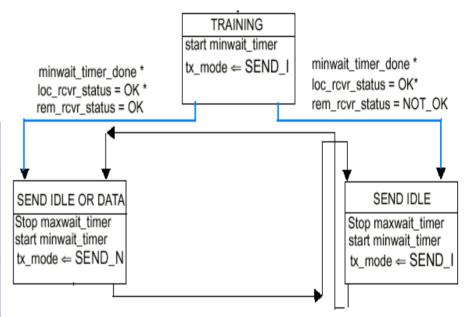

#### 40.4.6.1 PHY Control state diagram

The transition from SLAVE SILENT to the TRAINING state is determined by which mode SLAVE. the PHY is operating in SILENT (Master/Slave) start maxwait timer tx mode ← SEND Z If Master mode, the transition is instant config = MASTER + If Slave mode, the SLAVE PHY Converges scr\_status = OK the Decision Feedback Equalizer (DFE), TRAINING acquires timing, acquires a descrambler state, and sets scr status=OK. start minwait timer tx mode ← SEND I Once in this state, the minimum wait timer is started and the device is forced to transmit idle. The purpose of the

training state is to converge the adaptive filter parameters

UNIVERSITY of NEW HAMPSHIRE INTEROPERABILITY LABORATORY

- After the TRAINING state the PHY Control transitions into either the "SEND IDLE OR DATA" or "SEND IDLE" State. The conditions that determine this move are:

- minimum wait timer expires, status of the overall receive link(loc\_rcvr\_status), and the detection of a reliable remote PHY.

IF a reliable remote PHY is not detected

(rem\_rcvr\_status=NOT\_OK)

**THEN** the PHY control goes to the SEND IDLE state, where the Maximum wait timer is stopped, the Minimum wait timer is started, and the PHY is forced to transmit IDLE

**ELSE-IF** a reliable remote PHY is detected (rem\_rcvr\_status=OK)

**THEN** the PHY Control goes to the SEND IDLE OR DATA state where max wait is stopped, min wait is started, and it is granted the ability to transmit data or idle if no data is present

UNIVERSITY of NEW HAMPSHIRE INTEROPERABILITY LABORATORY

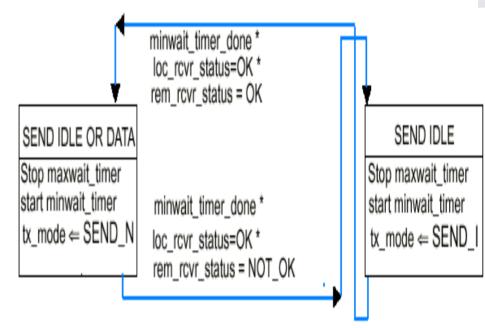

• If at any point during these two states given the min wait timer is done and receive status is good:

IF in SEND IDLE OR DATA state and the PHY detects an unsatisfactory remote receiver the transmission of data will finish and the PHY control will enter the SEND IDLE state

**IF** in the SEND IDLE state and the PHY detects a satisfactory remote receiver PHY Control will enter the SEND IDLE or DATA state.

## **PMA Function: PHY Control**

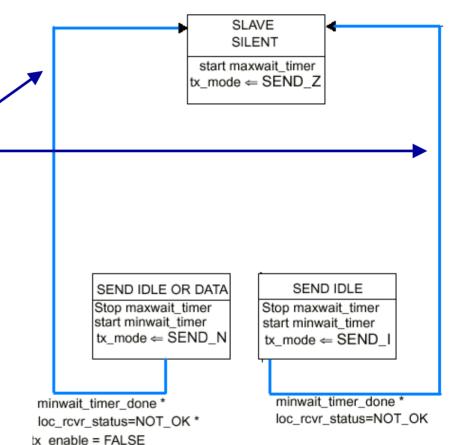

At any point in the SEND IDLE or SEND IDLE or DATA state if the min wait timer expires and the local PHY receiver status becomes unstable, the PHY control is directed back to the SLAVE SILENT state after completing transmission of the current frame.

This effectively restarts the PHY control process

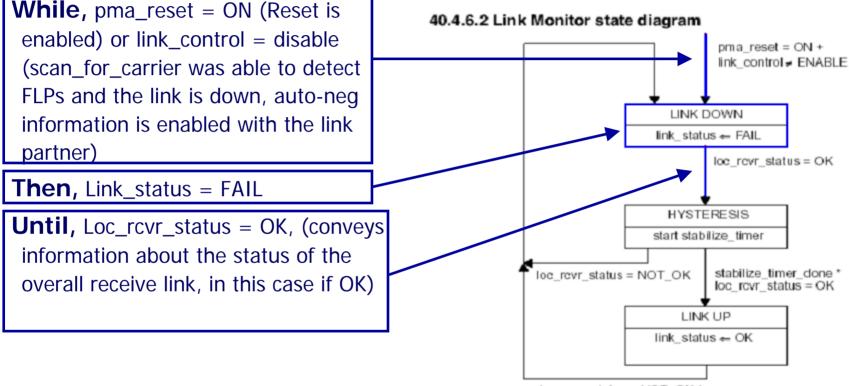

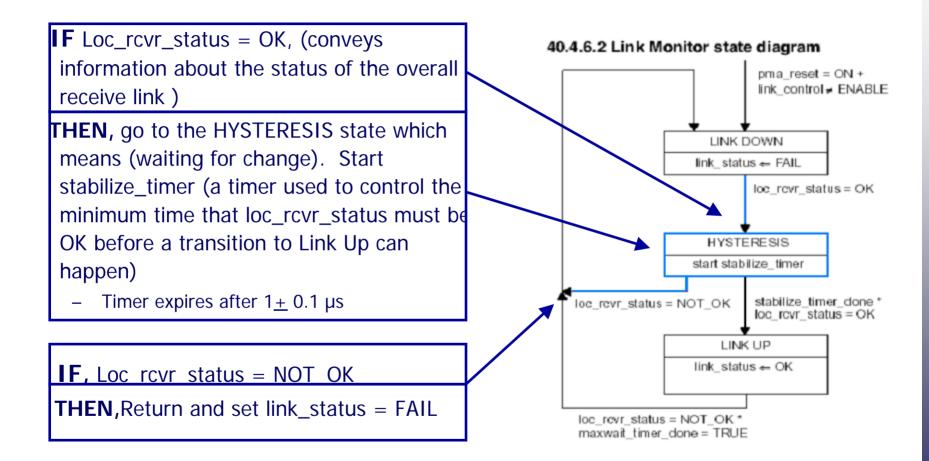

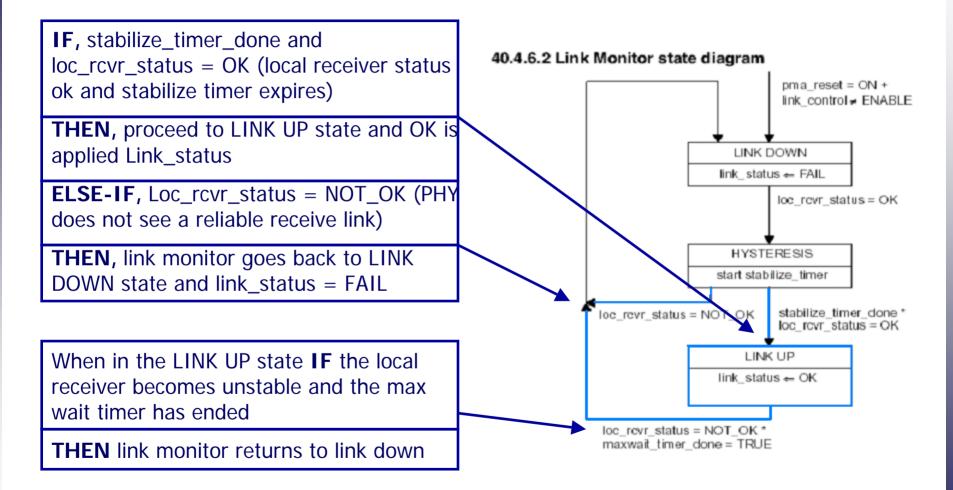

- Determines the status of the underlying receive channel by communicating via the Link\_status

- Auto-Negotiation sets the Link\_control depending on the reception of FLPs

- This function is better described by the following state diagram:

loc\_rcvr\_status = NOT\_OK \* maxwait\_timer\_done = TRUE

# PMA Functions: Clock Recovery

- Recovers the clock from the received stream

- Coupled to all four receive pairs

- Can provide independent clock phases for sampling signals on each pair

- Provides a suitable clock for signal sampling on each line to achieve the symbol error rate

- Used as an input variable for other PMA Functions

#### **PMA Electrical**

• PMA Electrical is broken into several parts:

- Isolation requirements

- Test Channel setup

- 4 Test Modes

- Transmitter Distortion

- Transmitter Timing Jitter

### PMA Electrical: Isolation

- Isolation Requirement:

- The PHY shall provide electrical isolation between the port device circuit and all MDI leads and withstand the following stress tests:

- 1500 V rms at 50 Hz to 60 Hz for 60 s

- 2250 Vdc for 60 s

- A sequence of ten 2400 V impulses of alternating polarity, applied at intervals of not less than 1 s

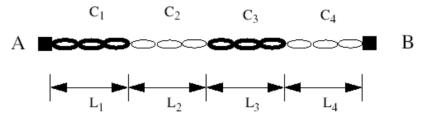

### PMA Electrical: Test Channel

- Transmitter MASTER-SLAVE timing jitter test require a Test Channel to ensure the signal is measured under conditions of poor signal echo ratio constructed from 100 and 120 Ohm Cat5 cable

- Shown at right is the Test channel topology and the Test channel Cable Specifications

Identical for each of the four pairs.

|               | • •                  |                                                            |                                                 |  |

|---------------|----------------------|------------------------------------------------------------|-------------------------------------------------|--|

| Cable segment | Length<br>(meters)   | Characteristic<br>impedance<br>(at frequencies<br>> 1 MHz) | Attenuation<br>(per 100 meters<br>at 31.25 MHz) |  |

| 1             | L <sub>1</sub> =1.20 | $120 \pm 5\Omega$                                          | 7.8 to 8.8 dB                                   |  |

| 2             | L <sub>2</sub> =x    | $100 \pm 5\Omega$                                          | 10.8 to 11.8 dB                                 |  |

| 3             | L <sub>3</sub> =1.48 | $120 \pm 5\Omega$                                          | 7.8 to 8.8 dB                                   |  |

| 4             | L <sub>4</sub> =y    | $100 \pm 5\Omega$                                          | 10.8 to 11.8 dB                                 |  |

#### Table 40–6–Test channel cable segment specifications

- There are four test modes that shall be provided by the PMA to allow testing of:

- transmitter waveform, transmitter distortion, and transmitted jitter.

- These Test Modes can be enabled by setting bits 9.13:15 (1000Base-T Control Register)

- These Test Modes shall only change the data symbols provided to the transmitter circuitry and shall not alter the electrical and jitter characteristics of the transmitter and receiver from those of normal (non-test mode) operation.

- At right are the Bit assignments to access the 4 PMA Test Modes.

- These modes are enabled by setting bits 9.13:15 if the device is equipped with a GMII interface.

- These test modes should only change the data symbols provided by the transmitter circuitry and shall not alter the electrical and jitter characteristics of the transmitter and receiver

UNIVERSITY of NEW HAMPSHIRE INTEROPERABILITY LABORATORY

#### Table 40–7 – GMII management register settings for test modes

| Bit 1<br>(9.15) | Bit 2<br>(9.14) | Bit 3<br>(9.13) | Mode                                            |

|-----------------|-----------------|-----------------|-------------------------------------------------|

| 0               | 0               | 0               | Normal operation                                |

| 0               | 0               | 1               | Test mode 1-Transmit waveform test              |

| 0               | 1               | 0               | Test mode 2-Transmit jitter test in MASTER mode |

| 0               | 1               | 1               | Test mode 3-Transmit jitter test in SLAVE mode  |

| 1               | 0               | 0               | Test mode 4-Transmitter distortion test         |

| 1               | 0               | 1               | Reserved, operations not identified.            |

| 1               | 1               | 0               | Reserved, operations not identified.            |

| 1               | 1               | 1               | Reserved, operations not identified.            |

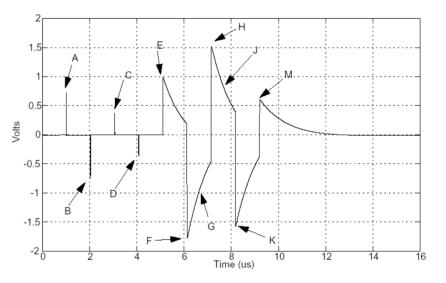

- In test mode 1 the PHY shall transmit the following sequence on all four transmitters continually from a 125MHz clock in MASTER timing mode:

- {{+2 followed by 127 0 symbols}, {-2 followed by 127 0 symbols}, {+1 followed by 127 0 symbols}, {-1 followed by 127 0 symbols}, {128 +2 symbols, 128 -2 symbols, 128 +2 symbols, 128 -2 symbols}, {1024 0 symbols}}

- At right is the typical wave form shape with the 11 letters representing points that are used for further reference:

- -A = +2s; B = -2s; C = +1s

- D = -1s; ...

- (where s is Symbol)

Figure 40–19—Example of transmitter test mode 1 waveform (1 cycle)

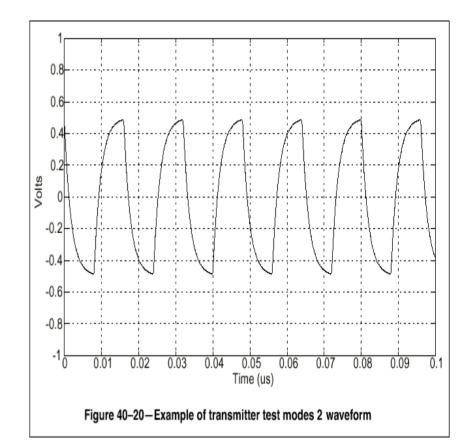

- The PHY transmits a data symbol sequence of {+2,-2} repeatedly on all channels with a signal clock of 125 Mhz in <u>MASTER</u> timing mode.

- At right is the typical Test mode 2 waveform

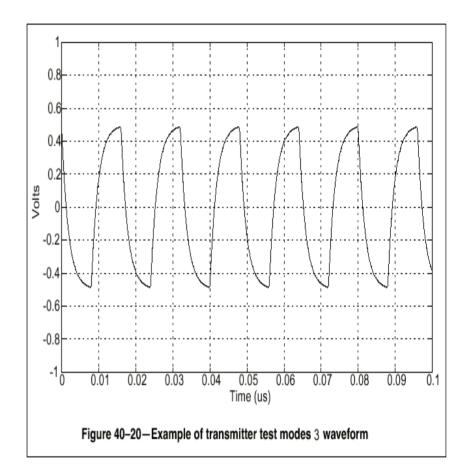

- The PHY transmits a data symbol sequence of {+2,-2} repeatedly on all channels with a signal clock of 125 Mhz in <u>SLAVE</u> timing mode.

- At right is the typical Test mode 3 waveform

- Note: This is the same wave from as Test Mode 2 because of the identical symbol sequence

When Test mode 4 is enabled, the PHY transmits a sequence of symbols generated by the following scrambler polynomial:

$- g_{s1} = 1 + x^9 + x^{11}$

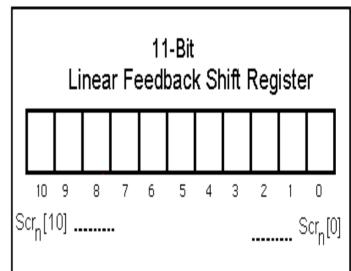

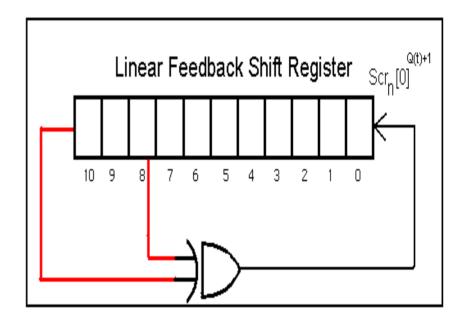

The 11-Bit Linear Feedback Shift Register used to generate this sequence is shown at right. This shift register is loaded with an initial "Symbol Map" at start up.

- The Linear Feedback Shift Register is updated once every symbol interval

8 ns, or 1/125MHz

- At every interval the shift register is advanced one bit to the left and generates a new bit as shown:

- $Scr_n[0] \leftarrow Scr_n[10] \bigoplus Scr_n[8]$

- Three Bit sequences (x0<sub>n</sub>, x1<sub>n</sub>, and x2<sub>n</sub>) are made form the equations shown at upper right and the respective bits held in the 11-bit Shift Register.

- These three bit sequences are then matched to a symbol map that equates the three bit sequence to a quinary symbol as shown at lower right:

$$x0_n = Scr_n[0]$$

$$x1_n = Scr_n[1] \wedge Scr_n[4]$$

$$x2_n = Scr_n[2] \wedge Scr_n[4]$$

| x2n | x1n | x0n | quinary<br>symbol, s <sub>n</sub> |

|-----|-----|-----|-----------------------------------|

| 0   | 0   | 0   | 0                                 |

| 0   | 0   | 1   | 1                                 |

| 0   | 1   | 0   | 2                                 |

| 0   | 1   | 1   | -1                                |

| 1   | 0   | 0   | 0                                 |

| 1   | 0   | 1   | 1                                 |

| 1   | 1   | 0   | -2                                |

| 1   | 1   | 1   | -1                                |

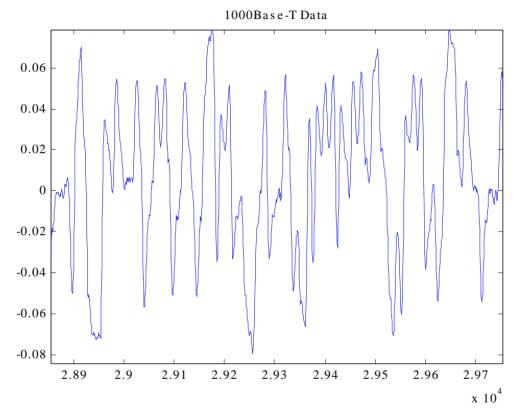

Shown below is the typical test mode 4 output. What would be normally 5 levels is shown as a pseudo random 17 level waveform after partial response is applied.

#### PMA Electrical: Transmitter Distortion

- Transmitter Distortion is a measured with the device in Test Mode 4 by observing the differential signal output at the MDI on each pair.

- The peak distortion shall not exceed 10 mV (as defined by 802.3).

- Peak Distortion is determined by comparing the received sequence with the ideal waveform.

#### PMA Electrical: Transmitter Timing Jitter

• Jitter is the difference between the time that an event was expected to occur and the time that the event actually occurred. In the context of a digital communications link, jitter is the offset between the expected position of a signal transition and the actual position of the transition. The magnitude of these offsets must be limited in order to limit the chances of an error on the link.

#### PMA Electrical: Transmitter Timing Jitter

- Jitter is the measure of the peak-to-peak deviations in time of the zero crossings of the differential signal output at the MDI relative to the corresponding edge of the transmit clock.

- The transmit clock edge is defined as the edge of the test clock with matching polarity and time that generates the zero-crossing transitions that are measured.

# In Summary

- PMA is primarily used to serialize and de-serialize the incoming data stream

- Acts as digital filter by applying partial response

- Converts the 5 level encoding known as PAM-5 into 5 discrete voltage levels

- PMA is also responsible for many of the Transmitter electrical characteristics such as Timing Jitter and Distortion

#### Additional resources

- IEEE 802.3-2002 Standard

- 1000Base-T PMA Test Suite

- 100Base-TX PMD Test Suite

- Beckwith's Brain/Plante's Brain

- Gary Pressler's Presentations